intel Agilex lojik etalaj blòk ak modil lojik adaptab

Intel® Agilex™ LAB ak ALM Overview

Blòk lojik etalaj la (LAB) konpoze de blòk bilding debaz ke yo rekonèt kòm modil lojik adaptasyon (ALMs). Ou ka configured LAB yo pou aplike fonksyon lojik, fonksyon aritmetik, ak fonksyon anrejistreman.

Ou ka itilize mwatye nan LAB ki disponib nan aparèy Intel® Agilex™ kòm LAB memwa (MLABs). Sèten aparèy ka gen yon pi gwo rapò MLAB.

Lojisyèl Intel Quartus® Prime a ak lòt zouti sentèz twazyèm pati ki sipòte otomatikman chwazi mòd apwopriye pou fonksyon komen tankou kontè, sipè, soustrè, ak fonksyon aritmetik.

Intel Hyperflex™ Nwayo Achitekti, Intel Agilex Device Overview

Bay plis enfòmasyon sou Hyper-Registers ak achitekti debaz Intel Hyperflex™. Hyper-Registers yo se rejis adisyonèl ki disponib nan chak segman routage entèkoneksyon atravè twal debaz la, ki gen ladan segman routage ki konekte ak antre ak rezilta LAB yo.

Enskri Intel Hyperflex™

Fanmi aparèy Intel Agilex la baze sou achitekti debaz Intel Hyperflex™.

Intel Agilex LAB a genyen rejis Intel Hyperflex ak lòt karakteristik ki fèt pou fasilite retiming. Rejis Intel Hyperflex yo disponib nan ALM ak chenn pote. Jan yo montre nan figi a Intel Agilex ALM Koneksyon Detay, rejis Intel Hyperflex yo sitiye sou klèr synchrone ak revèy pèmèt antre yo ogmante oswa diminye reta chemen an. Tout rejis Intel Hyperflex yo ka aktive epi yo kontwole pa lojisyèl Intel Quartus Prime pandan retiming.

Intel Agilex LAB ak ALM Achitekti ak Karakteristik

Seksyon sa yo dekri LAB ak ALM pou aparèy Intel Agilex.

LAB

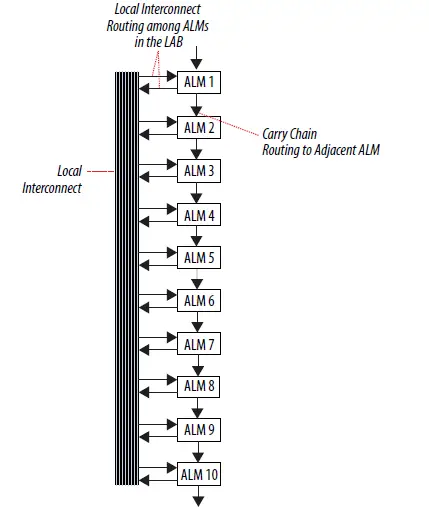

LAB yo se blòk lojik configurable ki konpoze de yon gwoup resous lojik. Chak LAB gen lojik dedye pou kondwi siyal kontwòl nan ALM li yo. MLAB a se yon superset nan LAB a epi li gen ladan tout karakteristik LAB yo. Gen yon total de 10 ALM nan chak LAB, jan yo montre nan figi Intel Agilex LAB ak Estrikti MLAB.

Figi 1.

Estrikti Intel Agilex LAB ak entèkoneksyon yo finiview

Figi sa a montre yon souview nan Intel Agilex LAB ak estrikti MLAB ak entèrkonèksyon LAB yo.

Enfòmasyon ki gen rapò

Enfòmasyon ki gen rapò

MLAB nan paj 6

MLAB

Chak MLAB sipòte yon maksimòm de 640 Bits nan senp doub-pò SRAM. Ou ka configured chak ALM nan yon MLAB kòm yon blòk memwa 32 (pwofondè) x 2 (lajè), sa ki lakòz yon konfigirasyon 32 (pwofondè) x 20 (lajè) senp blòk SRAM doub-pò.

Figi 2.

Intel Agilex LAB ak Estrikti MLAB Entèkonèksyon Lyen Lokal ak Dirèk

Entèkonèksyon Lyen Lokal ak Dirèk

Chak LAB ka mete 60 rezilta ALM. Yon sou-ansanm sa yo ka dirèkteman kondwi entrain LAB, men nenpòt koneksyon ak yon ranje oswa kolòn diferan dwe itilize omwen yon fil routage jeneral.

Koneksyon lokal la kondwi entrées ALM yo. ALM sorties, osi byen ke kolòn ak ranje interconnections kondwi interconnect lokal la.

Figi 3. Intel Agilex LAB Lokal ak Direct Link Interconnect  Pote chèn entèkoneksyon

Pote chèn entèkoneksyon

Gen yon chemen chèn devwe pote ant ALM yo. Aparèy Intel Agilex yo genyen yon estrikti entèkoneksyon amelyore nan LAB yo pou routage chenn pote pou fonksyon aritmetik efikas. Koneksyon ALM-a-ALM sa yo kontoune entèkoneksyon lokal la.

Rejis Intel Hyperflex yo ajoute nan chèn pote pou pèmèt retiming fleksib atravè yon chèn LAB yo epi Intel Quartus Prime Compiler otomatikman pran avans.tage nan resous sa yo amelyore itilizasyon ak pèfòmans.

Figi 4. Pote chèn entèkoneksyon Siyal kontwòl LAB

Siyal kontwòl LAB

Gen de sous revèy nan chak blòk kontwòl LAB, ki jenere de revèy LAB (LABCLK[1:0]) ak de revèy LAB reta (LABCLK_Phi1[1:0]) pou kondwi rejis ALM yo ak Hyper-Registers nan LAB la. LAB a sipòte de siyal inik revèy pèmèt, osi byen ke siyal adisyonèl klè, pou rejis ALM yo.

Revèy ranje LAB yo [5..0] ak entèkoneksyon lokal LAB yo jenere siyal kontwòl lajè LAB yo. Yon rezo revèy skew ki ba distribye siyal mondyal nan revèy yo ranje [5..0]. Entèkonèksyon MultiTrack a konsiste de liy routage kontinyèl ak pèfòmans-optimize nan longè diferan ak vitès yo itilize pou efikasite routage. Intel Quartus Prime Compiler otomatikman trase chemen konsepsyon kritik yo sou entèkoneksyon pi rapid pou amelyore pèfòmans konsepsyon ak optimize resous aparèy yo.

Klè kontwòl lojik

Siyal LAB-lajè kontwole lojik pou siyal klè rejis ALM la. Rejis ALM a dirèkteman sipòte tou de yon synchrone ak yon asynchrone klè. Chak LAB sipòte yon siyal klè synchrone ak de siyal klè asynchrone.

Aparèy Intel Agilex yo bay yon PIN reset nan tout aparèy (DEV_CLRn) ki reset tout rejis nan aparèy la. Ou ka aktive PIN DEV_CLRn nan lojisyèl Intel Quartus Prime anvan konpilasyon. Siyal reset nan tout aparèy la pase plis pase tout lòt siyal kontwòl yo.

Figi 5. Intel Agilex LAB-Wide siyal kontwòl

ALM

Seksyon sa yo kouvri resous ALM yo, pwodiksyon ALM, ak mòd operasyon ALM yo.

Resous ALM

Chak ALM gen yon varyete de resous ki baze sou LUT ki ka divize ant de LUTs adaptive konbinezon (ALUTs), yon ajoute de-bit plen, ak kat rejis.

Avèk jiska uit entrées pou de ALUTs konbinezon yo, yon sèl ALM ka aplike divès konbinezon de fonksyon. Adaptabilite sa a pèmèt yon ALM konplètman konpatib ak kat achitekti LUT D '. Yon ALM kapab tou aplike yon sou-ansanm nan uit fonksyon opinyon.

Yon ALM gen kat rejis pwogramasyon. Chak rejis gen pò sa yo:

- Done nan

- Done soti

- Nòmal revèy LAB

- Reta LAB revèy

- Revèy pèmèt

- Synchrone klè

- Asynchrone klè

Siyal mondyal yo, broch jeneral I/O (GPIO), oswa nenpòt lojik entèn yo ka kondwi revèy la pèmèt siyal, revèy, ak asynchrone oswa synchrone siyal kontwòl klè nan yon rejis ALM. Revèy pèmèt siyal la gen priyorite sou siyal reset synchrone.

Pou fonksyon konbinezon, rejis yo iyore ak pwodiksyon tab la gade-up (LUT) ak ajouter kondwi dirèkteman nan rezilta yo nan yon ALM. De pwodiksyon rapid ki disponib pou 6 pwodiksyon LUT ak anba 5 pwodiksyon LUT pou kontoune pwodiksyon mux la epi konekte ak yon lòt LAB pou ajisteman chemen kritik.

Figi 6. Dyagram blòk wo nivo Intel Agilex ALM

Sòti ALM

Sòti ALM

Pwodiksyon jeneral routage nan chak ALM kondwi resous routage lokal, ranje, ak kolòn. Sis pwodiksyon ALM, ki gen ladan de chemen pwodiksyon rapid, ka kondwi kolòn, ranje, oswa koneksyon dirèk routage lyen.

LUT, vidè, oswa enskri pwodiksyon an ka kondwi pwodiksyon ALM yo. Tou de LUT la oswa vidè ak enskri ALM la ka kondwi soti nan ALM la ansanm.

Anbalaj anrejistreman amelyore itilizasyon aparèy la lè li pèmèt rejis ki pa gen rapò ak lojik konbinezon yo dwe chaje nan yon sèl ALM. ALM a kapab tou chase vèsyon ki anrejistre ak ki pa anrejistre nan pwodiksyon LUT oswa ajoute.

Figi sa a montre koneksyon Intel Agilex ALM. Nan Intel Quartus Prime Resource Property Editor, tout koneksyon ALM la senplifye. Lojisyèl Intel Quartus Prime pral dirije kèk wout entèn yo.

Figi 7. Intel Agilex ALM Koneksyon Detay ALM Operating Modes

ALM Operating Modes

Intel Agilex ALM opere nan nenpòt nan mòd sa yo:

- Mòd nòmal

- Mòd LUT pwolonje

- Mòd aritmetik

Mòd nòmal

Mòd nòmal pèmèt de fonksyon yo dwe aplike nan yon sèl Intel Agilex ALM, oswa yon sèl fonksyon ki rive jiska sis entrain.

Jiska uit done ki soti nan entèkoneksyon lokal LAB yo se antre nan lojik konbinezon an.

ALM a ka sipòte sèten konbinezon de fonksyon konplètman endepandan ak divès kalite konbinezon de fonksyon ki gen opinyon komen.

Intel Quartus Prime Compiler la otomatikman chwazi antre yo nan LUT la. ALM nan mòd nòmal sipòte anbalaj enskri.

Figi sa a montre yon konbinezon diferan koneksyon opinyon pou mòd LUT la. Nan konsepsyon ou a, lojisyèl Intel Quartus Prime ka bay non diferan opinyon pandan konpilasyon.

Figi 8. ALM nan mòd nòmal

Konbinezon fonksyon ki gen mwens antre pase sa yo montre yo sipòte tou. Pou egzanpample, konbinezon fonksyon ak nimewo sa a nan antre yo sipòte.

- 4 ak 3

- 3 ak 3

- 3 ak 2

- 5 ak 2

Pou anbalaj de fonksyon 5 antre nan yon sèl ALM, fonksyon yo dwe gen omwen de antre komen. Antre komen yo se dataa ak datab. Konbinezon yon fonksyon 4 antre ak yon fonksyon 5 antre mande pou yon sèl antre komen (swa dataa oswa datab).

Nan yon aparèy ki pa itilize, fonksyon ki ta ka mete nan yon sèl ALM ka aplike nan ALM separe pa lojisyèl Intel Quartus Prime pou reyalize pi bon pèfòmans posib. Kòm yon aparèy kòmanse ranpli, lojisyèl Intel Quartus Prime otomatikman itilize tout potansyèl Intel Agilex ALM la. Intel Quartus Prime Compiler otomatikman chèche fonksyon lè l sèvi avèk antre komen oswa fonksyon konplètman endepandan yo dwe mete nan yon sèl ALM pou fè itilizasyon efikas resous aparèy yo. Anplis de sa, ou ka manyèlman kontwole itilizasyon resous lè w fikse devwa kote yo.

Figi 9. 6-Antre LUT Mode Fonksyon nan mòd nòmal

Figi 10. 3-Antre LUT Mode Fonksyon nan mòd nòmal

Figi 10. 3-Antre LUT Mode Fonksyon nan mòd nòmal

done ak done b yo disponib pou anbalaj enskri.  Ou ka aplike nenpòt fonksyon opinyon twa a sis lè l sèvi avèk antre sa yo:

Ou ka aplike nenpòt fonksyon opinyon twa a sis lè l sèvi avèk antre sa yo:

- done

- datad0

- datac0

- datac1

- datad1

- donef

- dataa ak datab—kidonk dataa ak datab yo pataje atravè tou de LUT yo pou bay fleksibilite pou aplike yon fonksyon diferan nan chak LUT.

Tou de dataa ak datab antre yo sipòte karakteristik nan anbalaj enskri. Si ou aktive karakteristik anbalaj anrejistreman an, tou de antre donea ak doneb oswa youn nan antre yo kontoune LUT la epi dirèkteman manje nan rejis la, tou depann de mòd enskripsyon ki te itilize a. Pou aparèy Intel Agilex, kalite mòd rejis chaje sa yo sipòte:

- 5-antre LUT ak 1 chemen anrejistreman chaje

- 5-antre LUT ak 2 chemen anrejistreman chaje

- De 3-antre LUT ak 2 chemen anrejistreman chaje

LUT 3 antre ak 2 chemen anrejistreman chaje yo montre nan Fonksyon Mode LUT 3 Antre nan figi Mode Nòmal. Pou aparèy Intel Agilex, mòd LUT 6 antre pa sipòte karakteristik anbalaj anrejistreman an.

Mòd LUT pwolonje

Figi 11. Sipòte 8-Fonksyon Antre nan mòd LUT pwolonje

Sèten fonksyon 8-antre ka aplike nan yon sèl ALM lè l sèvi avèk tout antre LUT yo:

- done

- datad0

- datac0

- donea

- doneb

- datac1

- datad1

- donef

Nan mòd LUT pwolonje 8-antre, mòd enskripsyon chaje a sipòte, depi rejis chaje a pataje yon donea oswa opinyon done ak LUT 8-antre.

Mòd aritmetik

ALM nan mòd aritmetik sèvi ak de seri de 4-antre LUT ansanm ak de dedye plen ajoute. Adders devwe yo pèmèt LUT yo fè lojik pre-additeur. Se poutèt sa, chak ajoute ka ajoute pwodiksyon an nan de fonksyon 4-antre.

Mòd aritmetik ofri tou revèy pèmèt, kontwa pèmèt, synchrone leve ak desann kontwòl, ajoute ak soustraksyon kontwòl, ak synchrone klè.

Opsyon klè ak revèy pèmèt yo se siyal LAB-lajè ki afekte tout rejis nan LAB la. Ou ka endividyèlman enfim oswa aktive siyal sa yo pou chak pè rejis nan yon LUT adaptasyon (ALUT). Lojisyèl Intel Quartus Prime otomatikman mete nenpòt rejis kontwa a pa itilize nan lòt LAB yo.

Figi 12. Intel Agilex ALM nan mòd aritmetik

Pote chèn

Pote chèn

Chèn nan pote bay yon fonksyon pote rapid ant ajoute yo devwe nan mòd aritmetik la.

Karakteristik seleksyon 2-bit nan aparèy Intel Agilex divize reta pwopagasyon chenn pote ak ALM la. Chenn pote yo ka kòmanse swa nan premye ALM oswa sizyèm ALM nan yon LAB. Dènye siyal pote soti nan yon ALM, kote li manje nan lokal, ranje, oswa kolòn entèkoneksyon.

Istwa Revizyon Dokiman pou Gid Itilizatè Intel Agilex Logic Array Blocks and Adaptive Logic Modules

| Vèsyon dokiman an | Chanjman |

| 2022.05.24 | Mizajou figi: Intel Agilex ALM High-Level Block Diagram. |

| 2019.11.14 | Mete ajou deskripsyon an nan seksyon Siyal Kontwòl LAB yo. |

| 2019.10.01 |

|

| 2019.04.02 | Premye lage. |

Intel Corporation.

Tout dwa rezève. Intel, logo Intel ak lòt mak Intel yo se mak komèsyal Intel Corporation oswa filiales li yo. Intel garanti pèfòmans pwodwi FPGA ak semi-conducteurs li yo selon espesifikasyon aktyèl yo an akò ak garanti estanda Intel a, men li rezève dwa pou fè chanjman nan nenpòt pwodwi ak sèvis nenpòt ki lè san avètisman. Intel pa asime okenn responsablite oswa responsablite ki soti nan aplikasyon an oswa itilizasyon nenpòt enfòmasyon, pwodwi oswa sèvis ki dekri la a eksepte si Intel te dakò ekspreseman alekri. Yo konseye kliyan Intel yo pou yo jwenn dènye vèsyon espesifikasyon aparèy yo anvan yo konte sou nenpòt enfòmasyon ki pibliye epi anvan yo pase lòd pou pwodwi oswa sèvis yo.

*Yo ka reklame lòt non ak mak kòm pwopriyete lòt moun.

ISO

9001:2015

Anrejistre

Dokiman / Resous

|

intel Agilex lojik etalaj blòk ak modil lojik adaptab [pdfGid Itilizatè Blòk etalaj lojik Agilex ak modil lojik adaptab, Agilex, blòk etalaj lojik ak modil lojik adaptab, blòk etalaj ak modil lojik adaptab, modil lojik adaptab, modil lojik |