ICE Debugger pwogramè yo

ICE Debugger pwogramè yo

Gid itilizatè Pwogramasyon ak debogaj

Pwogramasyon ak debogaj

Atmel-ICE

GID ITIlizatè a

Debugger Atmel-ICE la

Atmel-ICE se yon zouti devlopman pwisan pou debogaj ak pwogramasyon ARM® Cortex®-M ki baze sou Atmel ®SAM ak Atmel AVR mikrokontwolè ak ® On-Chip Debug kapasite.

Li sipòte:

- Pwogramasyon ak debogaj sou chip tout mikwokontwolè Atmel AVR 32-bit sou tou de J.TAG ak aWire interfaces

- Pwogramasyon ak debogaj sou chip tout aparèy fanmi Atmel AVR XMEGA® sou tou de JTAG ak PDI 2-fil interfaces

- Pwogramasyon (JTAG, SPI, UPDI) ak debogaj nan tout mikrokontwolè Atmel AVR 8-bit ak sipò OCD sou swa J.TAG, debugWIRE oswa UPDI interfaces

- Pwogramasyon ak debogaj tout mikrokontwolè Atmel SAM ARM Cortex-M ki baze sou tou de SWD ak JTAG interfaces

- Pwogramasyon (TPI) nan tout mikrokontwolè Atmel tinyAVR® 8-bit ak sipò pou koòdone sa a

Konsilte lis aparèy yo sipòte nan Gid Itilizatè Atmel Studio pou jwenn yon lis konplè aparèy ak koòdone ki sipòte pa lage firmwèr sa a.

Entwodiksyon

1.1. Entwodiksyon nan Atmel-ICE la

Atmel-ICE se yon zouti devlòpman pwisan pou debogaj ak pwogramasyon ARM Cortex-M ki baze sou Atmel SAM ak Atmel AVR mikrokontroleur ak kapasite Debug On-Chip.

Li sipòte:

- Pwogramasyon ak debogaj sou chip nan tout mikrokontwolè Atmel AVR UC3 sou tou de JTAG ak aWire interfaces

- Pwogramasyon ak debogaj sou chip nan tout aparèy fanmi AVR XMEGA sou tou de JTAG ak PDI 2wire interfaces

- Pwogramasyon (JTAG ak SPI) ak debogaj tout mikrokontwolè AVR 8-bit ak sipò OCD sou tou de JTAG oswa debugWIRE interfaces

- Pwogramasyon ak debogaj tout mikrokontwolè Atmel SAM ARM Cortex-M ki baze sou tou de SWD ak JTAG interfaces

- Pwogramasyon (TPI) nan tout mikrokontwolè Atmel tinyAVR 8-bit ak sipò pou koòdone sa a

1.2. Atmel-ICE Karakteristik

- Konplètman konpatib ak Atmel Studio

- Sipòte pwogramasyon ak debogaj nan tout mikrokontwolè Atmel AVR UC3 32-bit

- Sipòte pwogramasyon ak debogaj nan tout aparèy AVR XMEGA 8-bit

- Sipòte pwogramasyon ak debogaj tout aparèy 8-bit Atmel megaAVR® ak tinyAVR ki gen OCD

- Sipòte pwogramasyon ak debogaj tout mikrokontwolè ki baze sou SAM ARM Cortex-M

- Sib opere voltage seri de 1.62V a 5.5V

- Trase mwens pase 3mA nan sib VTref lè w ap itilize koòdone debugWIRE ak mwens pase 1mA pou tout lòt entèfas.

- Sipòte JTAG frekans revèy soti nan 32kHz a 7.5MHz

- Sipòte frekans revèy PDI soti nan 32kHz a 7.5MHz

- Sipòte debugWIRE pousantaj baud soti nan 4kbit / s a 0.5Mbit / s

- Sipòte vitès baud aWire soti nan 7.5kbit/s rive 7Mbit/s

- Sipòte frekans revèy SPI soti nan 8kHz a 5MHz

- Sipòte pousantaj baud UPDI soti nan jiska 750kbit/s

- Sipòte frekans revèy SWD soti nan 32kHz a 10MHz

- USB 2.0 gwo vitès koòdone lame

- ITM seri tras kaptire jiska 3MB/s

- Sipòte DGI SPI ak USART interfaces lè yo pa debogaj oswa pwogramasyon

- Sipòte 10-pin 50-mil JTAG konektè ak tou de pinouts AVR ak Cortex. Kab sonde estanda a sipòte AVR 6-pin ISP/PDI/TPI 100-mil headers osi byen ke 10-pin 50-mil. Gen yon adaptè ki disponib pou sipòte headers 6-pin 50-mil, 10-pin 100-mil, ak 20-pin 100-mil. Gen plizyè opsyon twous ki disponib ak diferan kabl ak adaptè.

1.3. Kondisyon sistèm

Inite Atmel-ICE la mande pou yon anviwònman debogaj front-end Atmel Studio vèsyon 6.2 oswa pita enstale sou òdinatè w lan.

Atmel-ICE a ta dwe konekte ak òdinatè lame a lè l sèvi avèk kab USB yo bay la, oswa yon kab sètifye Micro-USB.

Kòmanse ak Atmel-ICE

2.1. Kontni Twous konplè

Twous konplè Atmel-ICE la gen atik sa yo:

- Atmel-ICE inite

- USB kab (1.8m, gwo vitès, Micro-B)

- Tablo adaptè ki gen 50-mil AVR, 100-mil AVR/SAM, ak 100-mil 20-pin SAM adaptè

- IDC kab plat ak 10-pin 50-mil konektè ak 6-pin 100-mil konektè

- 50-mil 10-pin mini kalma kab ak 10 x 100-mil priz

Figi 2-1. Atmel-ICE Kontni Twous konplè 2.2. Kontni Twous Debaz yo

2.2. Kontni Twous Debaz yo

Twous debaz Atmel-ICE la gen atik sa yo:

- Atmel-ICE inite

- USB kab (1.8m, gwo vitès, Micro-B)

- IDC kab plat ak 10-pin 50-mil konektè ak 6-pin 100-mil konektè

Figi 2-2. Kontni Twous Debaz Atmel-ICE 2.3. Kontni Twous PCBA

2.3. Kontni Twous PCBA

Twous Atmel-ICE PCBA a gen atik sa yo:

- Atmel-ICE inite san plastik encapsulation

Figi 2-3. Kontni Twous Atmel-ICE PCBA 2.4. Twous pyès rezèv

2.4. Twous pyès rezèv

Twous pyès rezèv sa yo disponib:

- Twous adaptè

- Twous kab

Figi 2-4. Kontni Twous adaptè Atmel-ICE 2.5. Twous souview

2.5. Twous souview

Opsyon pou twous Atmel-ICE yo montre yon dyagram isit la:

Figi 2-6. Atmel-ICE Kit Overview 2.6. Rasanble Atmel-ICE la

2.6. Rasanble Atmel-ICE la

Inite Atmel-ICE la anbake san okenn câbles tache. Yo bay de opsyon kab nan twous konplè a:

- 50-mil 10-pin IDC kab plat ak 6-pin ISP ak konektè 10-pin

- 50-mil 10-pin kab mini-kalma ak 10 x 100-mil priz

Figi 2-7. Atmel-ICE Cables Pou pifò rezon, kab plat IDC 50-mil 10-pin ka itilize, konekte swa natif natal nan konektè 10-pin oswa 6-pin li yo, oswa konekte atravè tablo adaptè a. Twa adaptè yo bay sou yon sèl ti PCBA. Adaptè sa yo enkli:

Pou pifò rezon, kab plat IDC 50-mil 10-pin ka itilize, konekte swa natif natal nan konektè 10-pin oswa 6-pin li yo, oswa konekte atravè tablo adaptè a. Twa adaptè yo bay sou yon sèl ti PCBA. Adaptè sa yo enkli:

- 100-mil 10-pin JTAG/SWD adaptè

- 100-mil 20-pin SAM JTAG/SWD adaptè

- 50-mil 6-pin SPI/debugWIRE/PDI/aWire adaptè

Figi 2-8. Adaptè Atmel-ICE Nòt:

Nòt:

Yon 50-mil JTAG adaptè pa te bay - sa a se paske 50-mil 10-pin IDC kab la ka itilize pou konekte dirèkteman nan yon 50-mil J.TAG header. Pou nimewo pati eleman yo itilize pou konektè 50-mil 10-pin, gade Nimewo Pati Atmel-ICE Target Connectors.

Antèt ISP/PDI 6-pin enkli kòm yon pati nan kab IDC 10-pin. Revokasyon sa a ka koupe si li pa obligatwa.

Pou rasanble Atmel-ICE ou a nan konfigirasyon default li yo, konekte kab IDC 10-pin 50-mil ak inite a jan yo montre anba a. Asire ou ke ou oryante kab la pou fil wouj la (pin 1) sou kab la aliyen ak endikatè a triyangilè sou senti ble a nan patiraj la. Kab la ta dwe konekte anwo nan inite a. Asire w ou konekte ak pò ki koresponn ak pinout sib ou a - AVR oswa SAM.

Figi 2-9. Koneksyon kab Atmel-ICE Figi 2-10. Atmel-ICE AVR Sond Koneksyon

Figi 2-10. Atmel-ICE AVR Sond Koneksyon

Figi 2-11. Atmel-ICE SAM Sond Koneksyon

Figi 2-11. Atmel-ICE SAM Sond Koneksyon 2.7. Ouvèti Atmel-ICE la

2.7. Ouvèti Atmel-ICE la

Nòt:

Pou operasyon nòmal, inite Atmel-ICE pa dwe louvri. Ouvèti inite a fè sou pwòp risk ou.

Yo ta dwe pran prekosyon anti-estatik.

Patiraj Atmel-ICE la konsiste de twa konpozan plastik separe - kouvèti anwo, kouvèti anba, ak senti ble - ki kase ansanm pandan asanble a. Pou louvri inite a, tou senpleman mete yon gwo tounvis plat nan ouvèti yo nan senti ble a, aplike kèk presyon anndan ak tòde dousman. Repete pwosesis la sou lòt twou snapper yo, epi kouvèti anwo a ap pete.

Figi 2-12. Louvri Atmel-ICE (1)

Figi 2-13. Louvri Atmel-ICE (2)

Figi 2-13. Louvri Atmel-ICE (2)

Figi 2-14. Louvri Atmel-ICE(3)

Figi 2-14. Louvri Atmel-ICE(3) Pou fèmen inite a ankò, tou senpleman aliman kouvèti anwo ak anba yo kòrèkteman, epi peze byen fèm ansanm.

Pou fèmen inite a ankò, tou senpleman aliman kouvèti anwo ak anba yo kòrèkteman, epi peze byen fèm ansanm.

2.8. Alimente Atmel-ICE la

Atmel-ICE a se Powered by otobis la USB voltage. Li mande pou mwens pase 100mA pou opere, epi se poutèt sa ka mache atravè yon mwaye USB. Ki ap dirije pouvwa a ap limen lè inite a konekte. Lè yo pa konekte nan yon pwogramasyon aktif oswa sesyon debogaj, inite a pral antre nan mòd konsomasyon ba-pouvwa konsève batri òdinatè w lan. Atmel-ICE pa ka koupe kouran - li ta dwe deploge lè li pa itilize.

2.9. Konekte ak òdinatè lame a

Atmel-ICE kominike prensipalman lè l sèvi avèk yon koòdone HID estanda, epi li pa mande pou yon chofè espesyal sou òdinatè lame a. Pou itilize fonksyonalite avanse Data Gateway nan Atmel-ICE, asire w ou enstale chofè USB a sou òdinatè lame a. Sa fè otomatikman lè w ap enstale lojisyèl devan Atmel bay gratis. Gade www.atmel.com pou plis enfòmasyon oswa pou telechaje dènye lojisyèl front-end la.

Atmel-ICE a dwe konekte nan yon pò USB ki disponib sou òdinatè lame a lè l sèvi avèk kab USB yo bay la, oswa apwopriye USB sètifye mikwo kab. Atmel-ICE a gen yon USB 2.0 kontwolè konfòme, epi li ka opere nan tou de mòd plen vitès ak gwo vitès. Pou pi bon rezilta, konekte Atmel-ICE dirèkteman nan yon sant gwo vitès ki konfòm USB 2.0 sou òdinatè lame a lè l sèvi avèk kab yo bay la.

2.10. Enstalasyon chofè USB

2.10.1. Windows

Lè w ap enstale Atmel-ICE a sou yon òdinatè ki gen Microsoft® Windows®, chofè USB a chaje lè Atmel-ICE a premye konekte.

Nòt:

Asire w ou enstale pakè lojisyèl devan yo anvan ou branche inite a pou premye fwa.

Yon fwa enstale avèk siksè, Atmel-ICE ap parèt nan manadjè aparèy la kòm yon "Aparèy Entèfas Imèn".

Konekte Atmel-ICE la

3.1. Konekte ak aparèy sib AVR ak SAM

Atmel-ICE ekipe ak de 50-mil 10-pin JTAG konektè. Tou de konektè yo dirèkteman konekte elektrik, men konfòme yo ak de pinouts diferan; AVR JTAG header ak header a ARM Cortex Debug. Konektè a ta dwe chwazi ki baze sou pinout la nan tablo sib la, epi yo pa kalite MCU sib la - pou egzanpampYon aparèy SAM ki monte nan yon pil AVR STK® 600 ta dwe itilize header AVR la.

Plizyè câblage ak adaptè yo disponib nan diferan twous Atmel-ICE yo. Yon souview nan opsyon koneksyon yo montre.

Figi 3-1. Opsyon Koneksyon Atmel-ICE Fil wouj la make PIN 1 nan konektè 10-pin 50-mil la. PIN 1 nan konektè 6-pin 100-mil la mete sou bò dwat la nan kle a lè konektè a wè nan kab la. PIN 1 nan chak konektè sou adaptè a make ak yon pwen blan. Figi ki anba a montre pinout kab debogaj la. Konektè ki make A ploge nan debogaj la pandan y ap ploge bò B nan tablo sib la.

Fil wouj la make PIN 1 nan konektè 10-pin 50-mil la. PIN 1 nan konektè 6-pin 100-mil la mete sou bò dwat la nan kle a lè konektè a wè nan kab la. PIN 1 nan chak konektè sou adaptè a make ak yon pwen blan. Figi ki anba a montre pinout kab debogaj la. Konektè ki make A ploge nan debogaj la pandan y ap ploge bò B nan tablo sib la.

Figi 3-2. Debug Kab Pinout

3.2. Konekte ak yon JTAG Sib

3.2. Konekte ak yon JTAG Sib

Atmel-ICE ekipe ak de 50-mil 10-pin JTAG konektè. Tou de konektè yo dirèkteman konekte elektrik, men konfòme yo ak de pinouts diferan; AVR JTAG header ak header a ARM Cortex Debug. Konektè a ta dwe chwazi ki baze sou pinout la nan tablo sib la, epi yo pa kalite MCU sib la - pou egzanpampyon aparèy SAM ki monte nan yon pil AVR STK600 ta dwe itilize header AVR la.

Pinout rekòmande pou 10-pin AVR JTAG konektè yo montre nan Figi 4-6. Pinout rekòmande pou konektè 10-pin ARM Cortex Debug montre nan Figi 4-2.

Koneksyon dirèk nan yon header estanda 10-pin 50-mil

Sèvi ak kab plat 50-mil 10-pin (ki enkli nan kèk twous) pou konekte dirèkteman nan yon tablo ki sipòte kalite header sa a. Sèvi ak pò a konektè AVR sou Atmel-ICE la pou tèt ak pinout AVR a, ak pò a konektè SAM pou header ki konfòme ak pinout header ARM Cortex Debug la.

Pinouts yo pou tou de pò konektè 10-PIN yo montre anba a.

Koneksyon nan yon header estanda 10-pin 100-mil

Sèvi ak yon adaptè estanda 50-mil pou 100-mil pou konekte ak tèt 100-mil. Yon tablo adaptè (ki enkli nan kèk twous) ka itilize pou objektif sa a, oswa altènativman JTAGKa adaptè ICE3 dwe itilize pou objektif AVR.

![]() Enpòtan:

Enpòtan:

J laTAGICE3 100-mil adaptè pa ka itilize ak pò a konektè SAM, depi broch 2 ak 10 (AVR GND) sou adaptè a yo konekte.

Koneksyon nan yon header koutim 100-mil

Si tablo sib ou a pa gen yon J 10-pin ki konfòmeTAG header nan 50- oswa 100-mil, ou ka kat jeyografik nan yon pinout koutim lè l sèvi avèk 10-pin "mini-kalma" kab la (ki enkli nan kèk twous), ki bay aksè a dis priz endividyèl 100-mil.

Koneksyon nan yon heade 20-pin 100-milr

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk sib ak yon header 20-pin 100-mil.

Tablo 3-1. Atmel-ICE JTAG Deskripsyon Pin

| Non | AVR peny pò | SAM peny pò | Deskripsyon |

| TCK | 1 | 4 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 5 | 2 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 9 | 8 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 3 | 6 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nTRST | 8 | – | Tès Reyajiste (si ou vle, sèlman sou kèk aparèy AVR). Yo itilize pou reset JTAG TAP kontwolè. |

| nSRST | 6 | 10 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 4 | 1 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 3mA nan pin sa a nan mòd debugWIRE ak mwens pase 1mA nan lòt mòd. |

| GND | 2, 10 | 3, 5, 9 | Tè. Tout dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

3.3. Konekte ak yon sib aWire

Koòdone aWire mande pou yon sèl liy done anplis VCC ak GND. Sou sib la liy sa a se liy nRESET, byenke debogaj la sèvi ak JTAG Liy TDO kòm liy done.

Pinout rekòmande pou konektè aWire 6-pin yo montre nan Figi 4-8.

Koneksyon nan yon header 6-pin 100-mil aWire

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 100-mil aWire.

Koneksyon nan yon header 6-pin 50-mil aWire

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil aWire.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Twa koneksyon obligatwa, jan sa dekri nan tablo ki anba a.

Tablo 3-2. Atmel-ICE aWire Pin Mapping

|

Atmel-ICE AVR pò pins |

Pin sib | Mini-kalma PIN |

a Pinout fil |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | DONE | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | 6 | ||

| PIN 7 (Pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

3.4. Konekte ak yon sib PDI

Pinout rekòmande pou konektè PDI 6-pin yo montre nan Figi 4-11.

Koneksyon nan yon header 6-pin 100-mil PDI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil PDI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande kat koneksyon, jan sa dekri nan tablo ki anba a.

![]() Enpòtan:

Enpòtan:

Pinout ki nesesè yo diferan de JTAGICE mkII JTAG sonde, kote PDI_DATA konekte ak zepeng 9. Atmel-ICE konpatib ak pinout Atmel-ICE, J.TAGICE3, AVR ONE!, ak AVR Dragon™ pwodwi yo.

Tablo 3-3. Atmel-ICE PDI Pin Mapping

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

a Pinout fil |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | DONE | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | 6 | ||

| PIN 7 (Pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

3.4 Konekte ak yon sib PDI

Pinout rekòmande pou konektè PDI 6-pin yo montre nan Figi 4-11.

Koneksyon nan yon header 6-pin 100-mil PDI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil PDI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande kat koneksyon, jan sa dekri nan tablo ki anba a.

![]() Enpòtan:

Enpòtan:

Pinout ki nesesè yo diferan de JTAGICE mkII JTAG sonde, kote PDI_DATA konekte ak zepeng 9. Atmel-ICE konpatib ak pinout Atmel-ICE, J.TAGICE3, AVR ONE!, ak AVR Dragon™ pwodwi yo.

Tablo 3-3. Atmel-ICE PDI Pin Mapping

| Atmel-ICE AVR pò pin | Pin sib | Mini-kalma PIN | Atmel STK600 PDI pinout |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | PDI_DATA | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | PDI_CLK | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

3.5 Konekte ak yon sib UPDI

Pinout rekòmande pou konektè UPDI 6-pin yo montre nan Figi 4-12.

Koneksyon nan yon header UPDI 6-pin 100-mil

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header UPDI 100-mil estanda.

Koneksyon nan yon header UPDI 6-pin 50-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header UPDI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Twa koneksyon obligatwa, jan sa dekri nan tablo ki anba a.

Tablo 3-4. Atmel-ICE UPDI Pin Mapping

| Atmel-ICE AVR pò pin | Pin sib | Mini-kalma PIN |

Atmel STK600 UPDI pinout |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | UPDI_DATA | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | [/RESET sans] | 6 | 5 |

| PIN 7 (Pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

3.6 Konekte ak yon sib debugWIRE

Pinout rekòmande pou konektè 6-pin debugWIRE (SPI) yo montre nan Tablo 3-6.

Koneksyon nan yon header 6-pin 100-mil SPI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil SPI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Twa koneksyon obligatwa, jan sa dekri nan Tablo 3-5.

Malgre ke koòdone debugWIRE a sèlman mande pou yon liy siyal (RESET), VCC ak GND pou opere kòrèkteman, li konseye pou gen aksè a konektè SPI konplè pou koòdone debugWIRE la ka aktive ak enfim lè l sèvi avèk pwogram SPI.

Lè DWEN fuse a pèmèt koòdone SPI a pase sou plas anndan an nan lòd pou modil la OCD gen kontwòl sou PIN RESET la. DebugWIRE OCD a kapab enfim tèt li tanporèman (sèvi ak bouton ki sou tab debogaj la nan dyalòg pwopriyete yo nan Atmel Studio), konsa lage kontwòl liy RESET la. Lè sa a, koòdone SPI a disponib ankò (sèlman si SPIEN fuse a pwograme), sa ki pèmèt DWEN fuse a pa pwograme lè l sèvi avèk koòdone SPI la. Si pouvwa a activer anvan fusible DWEN pa pwograme, modil la debugWIRE pral ankò pran kontwòl PIN RESET la.

Nòt:

Li trè konseye pou tou senpleman kite Atmel Studio okipe anviwònman ak netwaye nan DWEN fuse a.

Li pa posib pou itilize koòdone debugWIRE si lockbit yo sou aparèy AVR sib la pwograme. Toujou asire w ke lockbits yo efase anvan ou pwograme DWEN fuse a epi pa janm mete lockbits yo pandan y ap DWEN fuse a pwograme. Si tou de debugWIRE pèmèt fuse (DWEN) ak lockbits yo mete, yon moun ka itilize High Vol.tage Pwogramasyon pou fè yon efase chip, epi konsa efase lockbits yo.

Lè lockbits yo otorize koòdone debugWIRE la pral re-pèmèt. Entèfas SPI a sèlman kapab li fusibles, li siyati ak fè yon efase chip lè fusible DWEN pa pwograme.

Tablo 3-5. Atmel-ICE debugWIRE Pin Mapping

| Atmel-ICE AVR pò pin | Pin sib |

Mini-kalma PIN |

| PIN 1 (TCK) | 1 | |

| PIN 2 (GND) | GND | 2 |

| PIN 3 (TDO) | 3 | |

| PIN 4 (VTG) | VTG | 4 |

| PIN 5 (TMS) | 5 | |

| PIN 6 (nSRST) | RESET | 6 |

| PIN 7 (Pa konekte) | 7 | |

| PIN 8 (nTRST) | 8 | |

| PIN 9 (TDI) | 9 | |

| PIN 10 (GND) | 0 |

3.7 Konekte ak yon sib SPI

Pinout rekòmande pou konektè SPI 6-pin yo montre nan Figi 4-10.

Koneksyon nan yon header 6-pin 100-mil SPI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil SPI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

![]() Enpòtan:

Enpòtan:

Koòdone SPI a efektivman enfim lè debugWIRE pèmèt fuse (DWEN) pwograme, menm si SPIEN fuse tou pwograme. Pou re-aktive koòdone SPI a, yo dwe bay lòd 'enfim debugWIRE' pandan y ap nan yon sesyon debogaj debugWIRE. Enfim debugWIRE nan fason sa a mande pou fuse SPIEN a deja pwograme. Si Atmel Studio echwe pou enfim debugWIRE, li posib paske SPIEN fuse a PA pwograme. Si sa a se ka a, li nesesè yo sèvi ak yon wo-voltage pwogramasyon koòdone pou pwogram SPIEN fuse a.

![]() Info:

Info:

Se koòdone SPI a souvan refere yo kòm "ISP", depi li te premye koòdone nan pwogramasyon nan sistèm sou pwodwi Atmel AVR. Lòt koòdone yo disponib kounye a pou nan pwogramasyon nan sistèm.

Tablo 3-6. Atmel-ICE SPI Pin Mapping

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

SPI pinout |

| PIN 1 (TCK) | SCK | 1 | 3 |

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | MISO | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | / RESET | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | MOSI | 9 | 4 |

| PIN 10 (GND) | 0 |

3.8 Konekte ak yon sib TPI

Pinout rekòmande pou konektè TPI 6-pin yo montre nan Figi 4-13.

Koneksyon nan yon header 6-pin 100-mil TPI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 100-mil TPI.

Koneksyon nan yon header 6-pin 50-mil TPI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil TPI.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

Tablo 3-7. Atmel-ICE TPI Pin Map

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

TPI pinout |

| PIN 1 (TCK) | LÒJ | 1 | 3 |

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | DONE | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 |

| PIN 6 (nSRST) | / RESET | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

3.9 Konekte ak yon sib SWD

Koòdone ARM SWD la se yon sous-ensemble nan JTAG koòdone, fè pou sèvi ak TCK ak TMS broch yo, ki vle di ke lè konekte ak yon aparèy SWD, 10-pin J la.TAG konektè ka teknikman itilize. ARM JTAG ak AVR JTAG Konektè yo, sepandan, pa PIN-konpatib, kidonk sa a depann sou Layout nan tablo sib yo itilize. Lè w ap itilize yon STK600 oswa yon tablo k ap sèvi ak AVR JTAG pinout, yo dwe itilize pò konektè AVR sou Atmel-ICE la. Lè w konekte ak yon tablo, ki sèvi ak ARM JTAG pinout, yo dwe itilize pò konektè SAM sou Atmel-ICE la.

Pinout rekòmande pou konektè Cortex Debug 10-pin yo montre nan Figi 4-4.

Koneksyon nan yon header Cortex 10-pin 50-mil

Sèvi ak kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil Cortex.

Koneksyon nan yon header 10-pin 100-mil Cortex-layout

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header Cortex-pinout 100-mil.

Koneksyon nan yon header SAM 20-pin 100-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header SAM 20-pin 100-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR oswa SAM ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

Tablo 3-8. Atmel-ICE SWD Pin Mapping

| Non | AVR peny pò | SAM peny pò | Deskripsyon |

| SWDC LK | 1 | 4 | Serial Fil Debug Revèy. |

| SWDIO | 5 | 2 | Serial Fil Debug Done Antre / Sòti. |

| SWO | 3 | 6 | Sòti Fil Serial (si ou vle-pa aplike sou tout aparèy). |

| nSRST | 6 | 10 | Reyajiste. |

| VTG | 4 | 1 | Sib voltage referans. |

| GND | 2, 10 | 3, 5, 9 | Tè. |

3.10 Konekte ak Entèfas Gateway Done

Atmel-ICE sipòte yon Entèfas Gateway Done (DGI) limite lè debogaj ak pwogramasyon pa itilize. Fonksyonalite idantik ak sa yo jwenn sou twous Atmel Xplained Pro ki mache ak aparèy Atmel EDBG la.

Entèfas Gateway Done a se yon koòdone pou difizyon done ki sòti nan aparèy sib la nan yon òdinatè. Sa vle di kòm yon èd nan debogaj aplikasyon kòm byen ke pou demonstrasyon de karakteristik nan aplikasyon an kouri sou aparèy la sib.

DGI konsiste de plizyè chanèl pou difizyon done. Atmel-ICE sipòte mòd sa yo:

- USART

- SPI

Tablo 3-9. Atmel-ICE DGI USART Pinout

|

pò AVR |

pò SAM | DGI USART pin |

Deskripsyon |

| 3 | 6 | TX | Transmèt PIN soti nan Atmel-ICE nan aparèy la sib |

| 4 | 1 | VTG | Sib voltage (referans voltage) |

| 8 | 7 | RX | Resevwa PIN soti nan aparèy la sib nan Atmel-ICE |

| 9 | 8 | CLK | USART revèy |

| 2, 10 | 3, 5, 9 | GND | Tè |

Tablo 3-10. Atmel-ICE DGI SPI Pinout

|

pò AVR |

pò SAM | DGI SPI PIN |

Deskripsyon |

| 1 | 4 | SCK | SPI revèy |

| 3 | 6 | MISO | Mèt nan esklav soti |

| 4 | 1 | VTG | Sib voltage (referans voltage) |

| 5 | 2 | nCS | Chip chwazi aktif ba |

| 9 | 8 | MOSI | Mèt soti esklav nan |

| 2, 10 | 3, 5, 9 | GND | Tè |

![]() Enpòtan: Entèfas SPI ak USART pa ka itilize ansanm.

Enpòtan: Entèfas SPI ak USART pa ka itilize ansanm.

![]() Enpòtan: DGI ak pwogramasyon oswa debogaj pa ka itilize ansanm.

Enpòtan: DGI ak pwogramasyon oswa debogaj pa ka itilize ansanm.

Debogaj sou chip

4.1 Entwodiksyon

Debogaj sou chip

Yon modil debug sou chip se yon sistèm ki pèmèt yon pwomotè kontwole ak kontwole ekzekisyon sou yon aparèy soti nan yon platfòm devlopman ekstèn, anjeneral atravè yon aparèy ke yo rekonèt kòm yon debugger oswa adaptè debug.

Avèk yon sistèm OCD aplikasyon an ka egzekite pandan w ap kenbe karakteristik egzak elektrik ak distribisyon nan sistèm sib la, pandan w ap kapab sispann egzekisyon kondisyonèl oswa manyèlman epi enspekte koule pwogram ak memwa.

Kouri mòd

Lè nan mòd Run, ekzekisyon kòd la konplètman endepandan de Atmel-ICE la. Atmel-ICE pral kontinyèlman kontwole aparèy sib la pou wè si gen yon kondisyon kraze. Lè sa rive sistèm OCD a pral entèwoje aparèy la atravè koòdone debug li yo, ki pèmèt itilizatè a view eta entèn aparèy la.

Mòd sispann

Lè yo rive nan yon breakpoint, ekzekisyon pwogram lan sispann, men kèk I/O ka kontinye kouri tankou si pa gen okenn breakpoint ki te fèt. Pou egzanpample, asime ke yon transmisyon USART jis te inisye lè yo rive nan yon breakpoint. Nan ka sa a USART kontinye ap kouri a tout vitès pou konplete transmisyon an, menm si nwayo a nan mòd sispann.

Materyèl Breakpoints

Modil OCD sib la gen yon kantite konparatè kontwa pwogram ki aplike nan pyès ki nan konpitè. Lè kontwa pwogram lan matche ak valè ki estoke nan youn nan rejis konparezon yo, OCD a antre nan mòd sispann. Piske pwen rupture pyès ki nan konpitè mande pou pyès ki nan konpitè dedye sou modil OCD a, kantite pwen rupture ki disponib depann de gwosè modil OCD ki aplike sou sib la. Dabitid yon sèl comparateur pyès ki nan konpitè sa yo ' rezève' pa débogueur pou itilize entèn.

Lojisyèl Breakpoints

Yon breakpoint lojisyèl se yon enstriksyon BREAK ki mete nan memwa pwogram nan sou aparèy sib la. Lè enstriksyon sa a chaje, ekzekisyon pwogram lan ap kraze epi OCD a antre nan mòd sispann. Pou kontinye egzekisyon, yon kòmand "kòmanse" dwe bay nan OCD la. Se pa tout aparèy Atmel ki gen modil OCD ki sipòte enstriksyon BREAK la.

4.2 Aparèy SAM ak JTAG/SWD

Tout aparèy SAM prezante koòdone SWD pou pwogramasyon ak debogaj. Anplis de sa, kèk aparèy SAM prezante yon JTAG koòdone ak fonksyonalite ki idantik. Tcheke fichye done aparèy la pou interfaces ki sipòte aparèy sa a.

4.2.1.ARM CoreSight Components

Mikwokontroleur Atmel ARM Cortex-M ki baze sou aplike konpozan OCD ki konfòme CoreSight. Karakteristik yo nan eleman sa yo ka varye de aparèy nan aparèy. Pou plis enfòmasyon konsilte fichye aparèy la ansanm ak dokiman CoreSight ARM bay.

4.2.1. JTAG Entèfas fizik

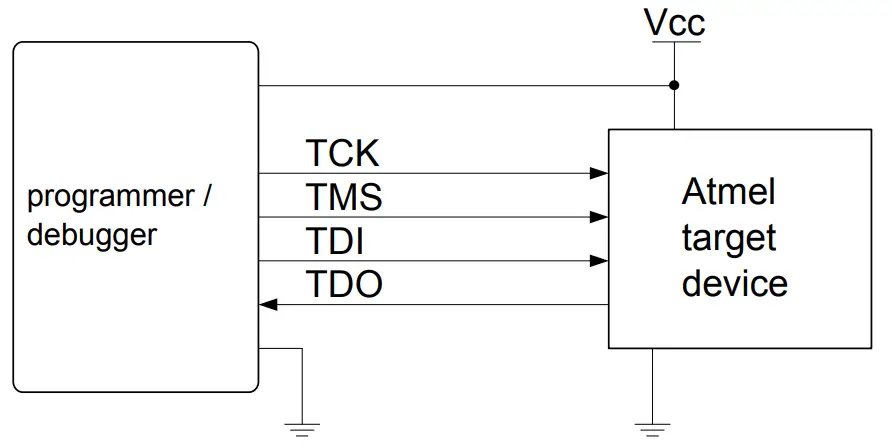

J laTAG koòdone konsiste de yon kontwolè 4-fil Tès Aksè Port (TAP) ki konfòme ak IEEE la® 1149.1 estanda. Yo te devlope estanda IEEE pou bay yon fason estanda endistri pou teste koneksyon tablo sikwi (Booundary Scan). Aparèy Atmel AVR ak SAM te pwolonje fonksyonalite sa a pou yo enkli tout sipò pwogramasyon ak debogaj sou chip.

Figi 4-1. JTAG Entèfas Prensip Fondamantal nan

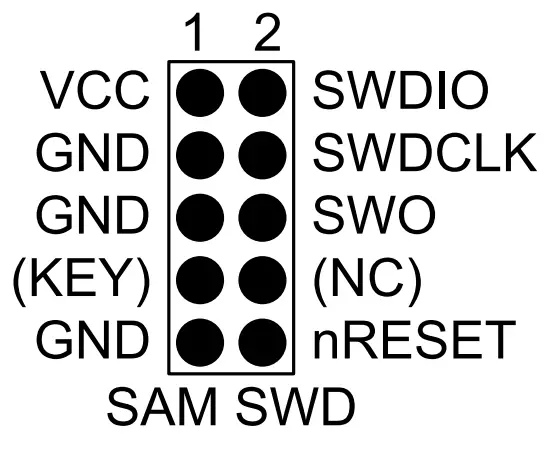

4.2.2.1 SAM JTAG Pinout (Konektè debug Cortex-M)

Lè w ap desine yon PCB aplikasyon ki gen ladann yon SAM Atmel ak JTAG koòdone, li rekòmande pou itilize pinout la jan yo montre nan figi ki anba a. Tou de 100-mil ak 50-mil varyant sa a pinout yo sipòte, tou depann de kabl la ak adaptè ki enkli ak twous la patikilye.

Figi 4-2. SAM JTAG Pinout header

Tablo 4-1. SAM JTAG Deskripsyon Pin

| Non | PIN |

Deskripsyon |

| TCK | 4 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 2 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 8 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 6 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nRESET | 10 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 1 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 1mA nan pin sa a nan mòd sa a. |

| GND | 3, 5, 9 | Tè. Tout dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

| KLE | 7 | Konekte intern ak PIN TRST sou konektè AVR la. Rekòmande kòm pa konekte. |

![]() Konsèy: Sonje mete yon kondansateur dekouplage ant PIN 1 ak GND.

Konsèy: Sonje mete yon kondansateur dekouplage ant PIN 1 ak GND.

4.2.2.2 JTAG Daisy Chaining

J laTAG koòdone pèmèt pou plizyè aparèy yo dwe konekte nan yon sèl koòdone nan yon konfigirasyon chèn Daisy. Aparèy sib yo dwe tout ap mache ak menm ekipman pou voltage, pataje yon ne tè komen, epi yo dwe konekte jan yo montre nan figi ki anba a.

Figi 4-3. JTAG Sou entènèt jwèt Daisy Chain

Lè w konekte aparèy nan yon chèn Daisy, yo dwe konsidere pwen sa yo:

- Tout aparèy yo dwe pataje yon baz komen, ki konekte ak GND sou sond Atmel-ICE la

- Tout aparèy dwe opere sou menm sib voltage. VTG sou Atmel-ICE dwe konekte ak vol sa atage.

- TMS ak TCK yo konekte nan paralèl; TDI ak TDO yo konekte nan yon seri

- nSRST sou sond Atmel-ICE la dwe konekte ak RESET sou aparèy yo si nenpòt nan aparèy yo nan chèn nan enfim J li yo.TAG pò

- "Aparèy anvan" refere a kantite JTAG aparèy ki siyal TDI a gen pou pase nan chenn Daisy la anvan yo rive nan aparèy sib la. Menm jan an tou "aparèy apre" se kantite aparèy ke siyal la dwe pase apre aparèy sib la anvan yo rive nan Atmel-ICE TDO.

- "Bis enstriksyon "anvan" ak "apre" refere a sòm total tout JTAG longè enskripsyon enstriksyon aparèy yo, ki konekte anvan ak apre aparèy la sib nan chèn nan Daisy

- Longè total IR (bit enstriksyon anvan + longè IR aparèy sib Atmel + bit enstriksyon apre) limite a yon maksimòm de 256 bit. Kantite aparèy nan chèn lan limite a 15 anvan ak 15 apre.

![]() Konsèy:

Konsèy:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Yo nan lòd yo konekte ak Atmel AVR XMEGA la® aparèy, paramèt Daisy Chain yo se:

- Aparèy anvan: 1

- Aparèy apre: 1

- Bits enstriksyon anvan: 4 (aparèy AVR 8-bit gen 4 bit IR)

- Bits enstriksyon apre: 5 (aparèy AVR 32-bit gen 5 Bits IR)

Tablo 4-2. IR Longè MCU Atmel yo

| Kalite aparèy | Longè IR |

| AVR 8-bit | 4 bit |

| AVR 32-bit | 5 bit |

| SAM | 4 bit |

4.2.3. Konekte ak yon JTAG Sib

Atmel-ICE ekipe ak de 50-mil 10-pin JTAG konektè. Tou de konektè yo dirèkteman konekte elektrik, men konfòme yo ak de pinouts diferan; AVR JTAG header ak header a ARM Cortex Debug. Konektè a ta dwe chwazi ki baze sou pinout la nan tablo sib la, epi yo pa kalite MCU sib la - pou egzanpampyon aparèy SAM ki monte nan yon pil AVR STK600 ta dwe itilize header AVR la.

Pinout rekòmande pou 10-pin AVR JTAG konektè yo montre nan Figi 4-6.

Pinout rekòmande pou konektè 10-pin ARM Cortex Debug montre nan Figi 4-2.

Koneksyon dirèk nan yon header estanda 10-pin 50-mil

Sèvi ak kab plat 50-mil 10-pin (ki enkli nan kèk twous) pou konekte dirèkteman nan yon tablo ki sipòte kalite header sa a. Sèvi ak pò a konektè AVR sou Atmel-ICE la pou tèt ak pinout AVR a, ak pò a konektè SAM pou header ki konfòme ak pinout header ARM Cortex Debug la.

Pinouts yo pou tou de pò konektè 10-PIN yo montre anba a.

Koneksyon nan yon header estanda 10-pin 100-mil

Sèvi ak yon adaptè estanda 50-mil pou 100-mil pou konekte ak tèt 100-mil. Yon tablo adaptè (ki enkli nan kèk twous) ka itilize pou objektif sa a, oswa altènativman JTAGKa adaptè ICE3 dwe itilize pou objektif AVR.

![]() Enpòtan:

Enpòtan:

J laTAGICE3 100-mil adaptè pa ka itilize ak pò a konektè SAM, depi broch 2 ak 10 (AVR GND) sou adaptè a yo konekte.

Koneksyon nan yon header koutim 100-mil

Si tablo sib ou a pa gen yon J 10-pin ki konfòmeTAG header nan 50- oswa 100-mil, ou ka kat jeyografik nan yon pinout koutim lè l sèvi avèk 10-pin "mini-kalma" kab la (ki enkli nan kèk twous), ki bay aksè a dis priz endividyèl 100-mil.

Koneksyon nan yon header 20-pin 100-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk sib ak yon header 20-pin 100-mil.

Tablo 4-3. Atmel-ICE JTAG Deskripsyon Pin

| Non | AVR peny pò | SAM peny pò | Deskripsyon |

| TCK | 1 | 4 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 5 | 2 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 9 | 8 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 3 | 6 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nTRST | 8 | – | Tès Reyajiste (si ou vle, sèlman sou kèk aparèy AVR). Yo itilize pou reset JTAG TAP kontwolè. |

| nSRST | 6 | 10 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 4 | 1 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 3mA nan pin sa a nan mòd debugWIRE ak mwens pase 1mA nan lòt mòd. |

| GND | 2, 10 | 3, 5, 9 | Tè. Tout dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

4.2.4. Entèfas fizik SWD

Koòdone ARM SWD la se yon sous-ensemble nan JTAG koòdone, fè pou sèvi ak TCK ak TMS broch. ARM JTAG ak AVR JTAG konektè yo, sepandan, pa PIN-konpatib, kidonk lè w ap desine yon PCB aplikasyon, ki sèvi ak yon aparèy SAM ak SWD oswa J.TAG koòdone, li rekòmande pou itilize pinout ARM yo montre nan figi ki anba a. Pò konektè SAM sou Atmel-ICE a ka konekte dirèkteman nan pinout sa a.

Figi 4-4. Rekòmande ARM SWD/JTAG Pinout header

Atmel-ICE a kapab difizyon tras ITM nan fòma UART sou òdinatè lame a. Tras kaptire sou PIN TRACE/SWO nan header 10-pin (JTAG PIN TDO). Done yo tampon entèn sou Atmel-ICE la epi yo voye sou koòdone HID nan òdinatè lame a. Pousantaj maksimòm done serye se sou 3MB/s.

4.2.5. Konekte ak yon sib SWD

Koòdone ARM SWD la se yon sous-ensemble nan JTAG koòdone, fè pou sèvi ak TCK ak TMS broch yo, ki vle di ke lè konekte ak yon aparèy SWD, 10-pin J la.TAG konektè ka teknikman itilize. ARM JTAG ak AVR JTAG Konektè yo, sepandan, pa PIN-konpatib, kidonk sa a depann sou Layout nan tablo sib yo itilize. Lè w ap itilize yon STK600 oswa yon tablo k ap sèvi ak AVR JTAG pinout, yo dwe itilize pò konektè AVR sou Atmel-ICE la. Lè w konekte ak yon tablo, ki sèvi ak ARM JTAG pinout, yo dwe itilize pò konektè SAM sou Atmel-ICE la.

Pinout rekòmande pou konektè Cortex Debug 10-pin yo montre nan Figi 4-4.

Koneksyon nan yon header Cortex 10-pin 50-mil

Sèvi ak kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil Cortex.

Koneksyon nan yon header 10-pin 100-mil Cortex-layout

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header Cortex-pinout 100-mil.

Koneksyon nan yon header SAM 20-pin 100-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header SAM 20-pin 100-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR oswa SAM ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

Tablo 4-4. Atmel-ICE SWD Pin Mapping

| Non | AVR peny pò | SAM peny pò | Deskripsyon |

| SWDC LK | 1 | 4 | Serial Fil Debug Revèy. |

| SWDIO | 5 | 2 | Serial Fil Debug Done Antre / Sòti. |

| SWO | 3 | 6 | Sòti Fil Serial (si ou vle-pa aplike sou tout aparèy). |

| nSRST | 6 | 10 | Reyajiste. |

| VTG | 4 | 1 | Sib voltage referans. |

| GND | 2, 10 | 3, 5, 9 | Tè. |

4.2.6 Konsiderasyon espesyal

EFASE PIN

Gen kèk aparèy SAM yo enkli yon PIN ERASE ki afime pou fè yon efase konplè chip ak déblotché aparèy ki mete sekirite a. Karakteristik sa a makonnen ak aparèy li menm ak kontwolè flash la epi li pa fè pati nwayo ARM la.

PIN ERASE a PA fè pati okenn header debug, epi Atmel-ICE la pa kapab revandike siyal sa a pou déblotché yon aparèy. Nan ka sa yo itilizatè a ta dwe fè efase a manyèlman anvan yo kòmanse yon sesyon debug.

Entèfas fizik JTAG koòdone

Liy RESET ta dwe toujou konekte pou Atmel-ICE kapab pèmèt JTAG koòdone.

SWD koòdone

Liy RESET ta dwe toujou konekte pou Atmel-ICE kapab pèmèt koòdone SWD la.

4.3 AVR UC3 Aparèy ak JTAG/aWire

Tout aparèy AVR UC3 prezante JTAG koòdone pou pwogramasyon ak debogaj. Anplis de sa, kèk aparèy AVR UC3 prezante koòdone aWire ak fonksyonalite ki idantik lè l sèvi avèk yon sèl fil. Tcheke fichye done aparèy la pou interfaces ki sipòte aparèy sa a

4.3.1 Atmel AVR UC3 On-chip Debug System

Sistèm Atmel AVR UC3 OCD la fèt an akò ak estanda Nexus 2.0 (IEEE-ISTO 5001™-2003), ki se yon estanda debug sou chip ki trè fleksib ak pwisan pou mikrokontroleur 32-bit. Li sipòte karakteristik sa yo:

- Nexus konfòm solisyon debug

- OCD sipòte nenpòt vitès CPU

- Sis pwogram kontwa pyès ki nan konpitè breakpoints

- De pwen rupture done

- Breakpoints yo ka configuré kòm pwen veye yo

- Pwen pyès ki nan konpitè yo ka konbine pou bay repo sou chenn yo

- Nimewo san limit nan pwen rupture pwogram itilizatè yo (itilize BREAK)

- An tan reyèl pwogram kontwa branch trase, tras done, tras pwosesis (sipòte sèlman pa debogaj ak pò kaptire tras paralèl)

Pou plis enfòmasyon konsènan sistèm AVR UC3 OCD a, konsilte Manyèl Referans Teknik AVR32UC yo, ki sitiye sou www.atmel.com/uc3.

4.3.2. JTAG Entèfas fizik

J laTAG koòdone konsiste de yon kontwolè 4-fil Tès Aksè Port (TAP) ki konfòme ak IEEE la® 1149.1 estanda. Yo te devlope estanda IEEE pou bay yon fason estanda endistri pou teste koneksyon tablo sikwi (Booundary Scan). Aparèy Atmel AVR ak SAM te pwolonje fonksyonalite sa a pou yo enkli tout sipò pwogramasyon ak debogaj sou chip.

Figi 4-5. JTAG Entèfas Prensip Fondamantal nan

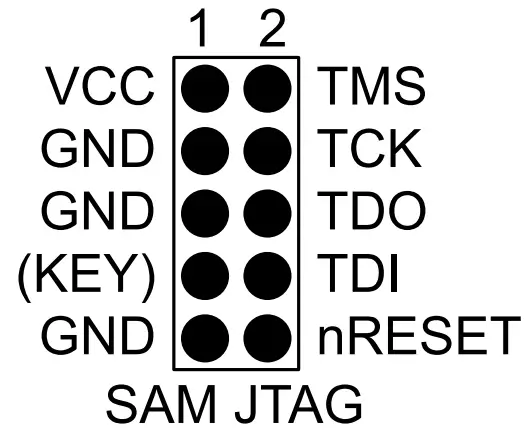

4.3.2.1 AVR JTAG Pinout

Lè w ap desine yon PCB aplikasyon, ki gen ladann yon AVR Atmel ak JTAG koòdone, li rekòmande pou itilize pinout la jan yo montre nan figi ki anba a. Tou de 100-mil ak 50-mil varyant sa a pinout yo sipòte, tou depann de kabl la ak adaptè ki enkli ak twous la patikilye.

Figi 4-6. AVR JTAG Pinout header

Tablo 4-5. AVR JTAG Deskripsyon Pin

| Non | PIN |

Deskripsyon |

| TCK | 1 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 5 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 9 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 3 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nTRST | 8 | Tès Reyajiste (si ou vle, sèlman sou kèk aparèy AVR). Yo itilize pou reset JTAG TAP kontwolè. |

| nSRST | 6 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 4 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 3mA nan pin sa a nan mòd debugWIRE ak mwens pase 1mA nan lòt mòd. |

| GND | 2, 10 | Tè. Tou de dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

![]() Konsèy: Sonje mete yon kondansateur dekouplage ant PIN 4 ak GND.

Konsèy: Sonje mete yon kondansateur dekouplage ant PIN 4 ak GND.

4.3.2.2 JTAG Daisy Chaining

J laTAG koòdone pèmèt pou plizyè aparèy yo dwe konekte nan yon sèl koòdone nan yon konfigirasyon chèn Daisy. Aparèy sib yo dwe tout ap mache ak menm ekipman pou voltage, pataje yon ne tè komen, epi yo dwe konekte jan yo montre nan figi ki anba a.

Figi 4-7. JTAG Sou entènèt jwèt Daisy Chain

Lè w konekte aparèy nan yon chèn Daisy, yo dwe konsidere pwen sa yo:

- Tout aparèy yo dwe pataje yon baz komen, ki konekte ak GND sou sond Atmel-ICE la

- Tout aparèy dwe opere sou menm sib voltage. VTG sou Atmel-ICE dwe konekte ak vol sa atage.

- TMS ak TCK yo konekte nan paralèl; TDI ak TDO yo konekte nan yon chèn seri.

- nSRST sou sond Atmel-ICE la dwe konekte ak RESET sou aparèy yo si nenpòt nan aparèy yo nan chèn nan enfim J li yo.TAG pò

- "Aparèy anvan" refere a kantite JTAG aparèy ki siyal TDI a gen pou pase nan chenn Daisy la anvan yo rive nan aparèy sib la. Menm jan an tou "aparèy apre" se kantite aparèy ke siyal la dwe pase apre aparèy sib la anvan yo rive nan Atmel-ICE TDO.

- "Bis enstriksyon "anvan" ak "apre" refere a sòm total tout JTAG longè enskripsyon enstriksyon aparèy yo, ki konekte anvan ak apre aparèy la sib nan chèn nan Daisy

- Longè total IR (bit enstriksyon anvan + longè IR aparèy sib Atmel + bit enstriksyon apre) limite a yon maksimòm de 256 bit. Kantite aparèy nan chèn lan limite a 15 anvan ak 15 apre.

Konsèy:

Daisy chaining example: TDI → ATmega1280 → ATxmega128A1 → ATUC3A0512 → TDO.

Yo nan lòd yo konekte ak Atmel AVR XMEGA la® aparèy, paramèt Daisy Chain yo se:

- Aparèy anvan: 1

- Aparèy apre: 1

- Bits enstriksyon anvan: 4 (aparèy AVR 8-bit gen 4 bit IR)

- Bits enstriksyon apre: 5 (aparèy AVR 32-bit gen 5 Bits IR)

Tablo 4-6. IR Longè Atmel MCUS

| Kalite aparèy | Longè IR |

| AVR 8-bit | 4 bit |

| AVR 32-bit | 5 bit |

| SAM | 4 bit |

4.3.3.Konekte ak yon JTAG Sib

Atmel-ICE ekipe ak de 50-mil 10-pin JTAG konektè. Tou de konektè yo dirèkteman konekte elektrik, men konfòme yo ak de pinouts diferan; AVR JTAG header ak header a ARM Cortex Debug. Konektè a ta dwe chwazi ki baze sou pinout la nan tablo sib la, epi yo pa kalite MCU sib la - pou egzanpampyon aparèy SAM ki monte nan yon pil AVR STK600 ta dwe itilize header AVR la.

Pinout rekòmande pou 10-pin AVR JTAG konektè yo montre nan Figi 4-6.

Pinout rekòmande pou konektè 10-pin ARM Cortex Debug montre nan Figi 4-2.

Koneksyon dirèk nan yon header estanda 10-pin 50-mil

Sèvi ak kab plat 50-mil 10-pin (ki enkli nan kèk twous) pou konekte dirèkteman nan yon tablo ki sipòte kalite header sa a. Sèvi ak pò a konektè AVR sou Atmel-ICE la pou tèt ak pinout AVR a, ak pò a konektè SAM pou header ki konfòme ak pinout header ARM Cortex Debug la.

Pinouts yo pou tou de pò konektè 10-PIN yo montre anba a.

Koneksyon nan yon header estanda 10-pin 100-mil

Sèvi ak yon adaptè estanda 50-mil pou 100-mil pou konekte ak tèt 100-mil. Yon tablo adaptè (ki enkli nan kèk twous) ka itilize pou objektif sa a, oswa altènativman JTAGKa adaptè ICE3 dwe itilize pou objektif AVR.

![]() Enpòtan:

Enpòtan:

J laTAGICE3 100-mil adaptè pa ka itilize ak pò a konektè SAM, depi broch 2 ak 10 (AVR GND) sou adaptè a yo konekte.

Koneksyon nan yon header koutim 100-mil

Si tablo sib ou a pa gen yon J 10-pin ki konfòmeTAG header nan 50- oswa 100-mil, ou ka kat jeyografik nan yon pinout koutim lè l sèvi avèk 10-pin "mini-kalma" kab la (ki enkli nan kèk twous), ki bay aksè a dis priz endividyèl 100-mil.

Koneksyon nan yon header 20-pin 100-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk sib ak yon header 20-pin 100-mil.

Tablo 4-7. Atmel-ICE JTAG Deskripsyon Pin

|

Non |

AVR pò PIN | PIN pò SAM |

Deskripsyon |

| TCK | 1 | 4 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 5 | 2 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 9 | 8 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 3 | 6 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nTRST | 8 | – | Tès Reyajiste (si ou vle, sèlman sou kèk aparèy AVR). Yo itilize pou reset JTAG TAP kontwolè. |

| nSRST | 6 | 10 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 4 | 1 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 3mA nan pin sa a nan mòd debugWIRE ak mwens pase 1mA nan lòt mòd. |

| GND | 2, 10 | 3, 5, 9 | Tè. Tout dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

4.3.4 aFil entèfas fizik

Koòdone aWire a sèvi ak fil RESET nan aparèy AVR a pou pèmèt fonksyon pwogramasyon ak debogaj. Yon sekans espesyal pèmèt Atmel-ICE transmèt, ki enfim fonksyonalite default RESET nan pin la. Lè w ap desine yon PCB aplikasyon, ki gen ladann yon AVR Atmel ak koòdone aWire, li rekòmande pou itilize pinout la jan yo montre nan Figi 4. -8. Tou de 100-mil ak 50-mil varyant sa a pinout yo sipòte, tou depann de kabl la ak adaptè ki enkli ak twous la patikilye.

Figi 4-8. aWire Header Pinout

![]() Konsèy:

Konsèy:

Depi aWire se yon koòdone demi-duplex, yon rezistans rale sou liy RESET nan lòd la nan 47kΩ rekòmande pou fè pou evite fo deteksyon kòmanse-bit lè chanje direksyon.

Ka koòdone nan aWire dwe itilize kòm tou de yon koòdone pwogramasyon ak debogaj. Tout karakteristik sistèm OCD disponib atravè 10-pin JTAG Ou ka jwenn aksè nan koòdone tou lè l sèvi avèk aWire.

4.3.5 Konekte ak yon sib aWire

Koòdone aWire mande pou yon sèl liy done anplis VCC ak GND. Sou sib la liy sa a se liy nRESET, byenke debogaj la sèvi ak JTAG Liy TDO kòm liy done.

Pinout rekòmande pou konektè aWire 6-pin yo montre nan Figi 4-8.

Koneksyon nan yon header 6-pin 100-mil aWire

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 100-mil aWire.

Koneksyon nan yon header 6-pin 50-mil aWire

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil aWire.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Twa koneksyon obligatwa, jan sa dekri nan tablo ki anba a.

Tablo 4-8. Atmel-ICE aWire Pin Mapping

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

a Pinout fil |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | DONE | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | 6 | ||

| PIN 7 (Pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

4.3.6. Konsiderasyon espesyal

JTAG koòdone

Sou kèk aparèy Atmel AVR UC3 JTAG pò pa aktive pa default. Lè w ap itilize aparèy sa yo, li esansyèl pou konekte liy RESET la pou Atmel-ICE kapab pèmèt JTAG koòdone.

aWire koòdone

Pousantaj baud kominikasyon aWire depann de frekans revèy sistèm lan, paske done yo dwe senkronize ant de domèn sa yo. Atmel-ICE pral otomatikman detekte ke revèy sistèm lan te bese, epi re-kalibre vitès baud li kòmsadwa. Kalibrasyon otomatik la sèlman travay jiska yon frekans revèy sistèm nan 8kHz. Chanje nan yon revèy sistèm pi ba pandan yon sesyon debug ka lakòz kontak ak sib la pèdi.

Si sa nesesè, pousantaj baud aWire ka limite lè w mete paramèt revèy aWire la. Deteksyon otomatik ap toujou travay, men yo pral enpoze yon valè plafon sou rezilta yo.

Nenpòt kondansateur estabilize ki konekte ak PIN RESET la dwe dekonekte lè w ap itilize aWire paske li pral entèfere ak operasyon kòrèk nan koòdone la. Yon pullup ekstèn fèb (10kΩ oswa pi wo) sou liy sa a rekòmande.

Fèmen mòd dòmi

Gen kèk aparèy AVR UC3 ki gen yon regilatè entèn ki ka itilize nan mòd ekipman pou 3.3V ak liy I/O reglemante 1.8V. Sa vle di ke regilatè a entèn pouvwa tou de nwayo a ak pi fò nan I / O la. Se sèlman Atmel AVR ONE! debugger sipòte debogaj pandan w ap itilize mòd dòmi kote regilatè sa a fèmen.

4.3.7. Itilizasyon EVTI / EVTO

Pin EVTI ak EVTO yo pa aksesib sou Atmel-ICE la. Sepandan, yo ka toujou itilize ansanm ak lòt ekipman ekstèn.

EVTI ka itilize pou rezon sa yo:

- Ka sib la dwe fòse yo sispann ekzekisyon an repons a yon evènman ekstèn. Si yo ekri bit Evènman nan kontwòl (EIC) nan rejis DC a nan 0b01, tranzisyon wo-ba sou pin EVTI a pral jenere yon kondisyon breakpoint. EVTI dwe rete ba pou yon sik revèy CPU pou garanti ke yon breakpoint se Bit The External Breakpoint Bit (EXB) nan DS yo mete lè sa rive.

- Jenere mesaj senkronizasyon tras. Atmel-ICE pa itilize.

EVTO ka itilize pou rezon sa yo:

- Ki endike ke CPU a te antre nan debug Mete EOS Bits nan DC a 0b01 lakòz PIN EVTO a dwe rale ba pou yon sik revèy CPU lè aparèy la sib antre nan mòd debug. Siyal sa a ka itilize kòm yon sous deklanche pou yon osiloskop ekstèn.

- Ki endike ke CPU a te rive nan yon breakpoint oswa watchpoint. Lè w mete bit EOC la nan yon Rejis Kontwòl Breakpoint/Watchpoint ki koresponn lan, yo endike estati pwen rupture a oswa pwen veye sou peny EVTO a. Bits EOS yo nan DC yo dwe mete sou 0xb10 pou pèmèt karakteristik sa a. Lè sa a, PIN EVTO a ka konekte ak yon osiloskop ekstèn yo nan lòd yo egzamine pwen veye

- Jenere tras siyal distribisyon. Atmel-ICE pa itilize.

4.4 aparèy tinyAVR, megaAVR ak XMEGA

Aparèy AVR prezante divès kalite koòdone pwogramasyon ak debogaj. Tcheke fichye done aparèy la pou interfaces ki sipòte aparèy sa a.

- Kèk tinyAVR® aparèy yo gen yon TPI TPI ka itilize pou pwogramasyon aparèy la sèlman, epi aparèy sa yo pa gen kapasite debug sou chip ditou.

- Gen kèk aparèy tinyAVR ak kèk aparèy megaAVR ki gen koòdone debugWIRE, ki konekte ak yon sistèm debug sou chip ke yo rekonèt kòm tinyOCD. Tout aparèy ak debugWIRE gen tou koòdone SPI pou nan sistèm nan

- Gen kèk aparèy megaAVR ki gen yon JTAG koòdone pou pwogramasyon ak debogaj, ak yon sistèm debug sou-chip ke yo rele tou Tout aparèy ak JTAG tou prezante koòdone SPI a kòm yon koòdone altènatif pou pwogram nan sistèm nan.

- Tout aparèy AVR XMEGA gen koòdone PDI pou pwogramasyon ak kèk aparèy AVR XMEGA gen tou yon J.TAG koòdone ak fonksyonalite ki idantik.

- Nouvo aparèy tinyAVR gen yon koòdone UPDI, ki itilize pou pwogramasyon ak debogaj

Tablo 4-9. Programming and Debugging Interfaces Rezime

|

|

UPDI | TPI | SPI | debugWIR E | JTAG | PDI | aFil |

SWD |

| tinyAVR | Nouvo aparèy | Gen kèk aparèy | Gen kèk aparèy | Gen kèk aparèy | ||||

| megaAV R | Tout aparèy | Gen kèk aparèy | Gen kèk aparèy | |||||

| AVR XMEGA | Gen kèk aparèy | Tout aparèy | ||||||

| AVR UC | Tout aparèy | Gen kèk aparèy | ||||||

| SAM | Gen kèk aparèy | Tout aparèy |

4.4.1. JTAG Entèfas fizik

J laTAG koòdone konsiste de yon kontwolè 4-fil Tès Aksè Port (TAP) ki konfòme ak IEEE la® 1149.1 estanda. Yo te devlope estanda IEEE pou bay yon fason estanda endistri pou teste koneksyon tablo sikwi (Booundary Scan). Aparèy Atmel AVR ak SAM te pwolonje fonksyonalite sa a pou yo enkli tout sipò pwogramasyon ak debogaj sou chip.

Figi 4-9. JTAG Entèfas Prensip Fondamantal nan 4.4.2. Konekte ak yon JTAG Sib

4.4.2. Konekte ak yon JTAG Sib

Atmel-ICE ekipe ak de 50-mil 10-pin JTAG konektè. Tou de konektè yo dirèkteman konekte elektrik, men konfòme yo ak de pinouts diferan; AVR JTAG header ak header a ARM Cortex Debug. Konektè a ta dwe chwazi ki baze sou pinout la nan tablo sib la, epi yo pa kalite MCU sib la - pou egzanpampyon aparèy SAM ki monte nan yon pil AVR STK600 ta dwe itilize header AVR la.

Pinout rekòmande pou 10-pin AVR JTAG konektè yo montre nan Figi 4-6.

Pinout rekòmande pou konektè 10-pin ARM Cortex Debug montre nan Figi 4-2.

Koneksyon dirèk nan yon header estanda 10-pin 50-mil

Sèvi ak kab plat 50-mil 10-pin (ki enkli nan kèk twous) pou konekte dirèkteman nan yon tablo ki sipòte kalite header sa a. Sèvi ak pò a konektè AVR sou Atmel-ICE la pou tèt ak pinout AVR a, ak pò a konektè SAM pou header ki konfòme ak pinout header ARM Cortex Debug la.

Pinouts yo pou tou de pò konektè 10-PIN yo montre anba a.

Koneksyon nan yon header estanda 10-pin 100-mil

Sèvi ak yon adaptè estanda 50-mil pou 100-mil pou konekte ak tèt 100-mil. Yon tablo adaptè (ki enkli nan kèk twous) ka itilize pou objektif sa a, oswa altènativman JTAGKa adaptè ICE3 dwe itilize pou objektif AVR.

![]() Enpòtan:

Enpòtan:

J laTAGICE3 100-mil adaptè pa ka itilize ak pò a konektè SAM, depi broch 2 ak 10 (AVR GND) sou adaptè a yo konekte.

Koneksyon nan yon header koutim 100-mil

Si tablo sib ou a pa gen yon J 10-pin ki konfòmeTAG header nan 50- oswa 100-mil, ou ka kat jeyografik nan yon pinout koutim lè l sèvi avèk 10-pin "mini-kalma" kab la (ki enkli nan kèk twous), ki bay aksè a dis priz endividyèl 100-mil.

Koneksyon nan yon header 20-pin 100-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk sib ak yon header 20-pin 100-mil.

Tablo 4-10. Atmel-ICE JTAG Deskripsyon Pin

| Non | AVR peny pò | SAM peny pò | Deskripsyon |

| TCK | 1 | 4 | Tès Clock (siyal revèy soti nan Atmel-ICE a nan aparèy la sib). |

| TMS | 5 | 2 | Tès Mode Chwazi (siyal kontwòl soti nan Atmel-ICE nan aparèy la sib). |

| TDI | 9 | 8 | Tès Done Nan (done transmèt soti nan Atmel-ICE a nan aparèy la sib). |

| TDO | 3 | 6 | Done tès soti (done transmèt soti nan aparèy la sib nan Atmel-ICE la). |

| nTRST | 8 | – | Tès Reyajiste (si ou vle, sèlman sou kèk aparèy AVR). Yo itilize pou reset JTAG TAP kontwolè. |

| nSRST | 6 | 10 | Reyajiste (si ou vle). Yo itilize pou Reyajiste aparèy la sib. Konekte pin sa a rekòmande paske li pèmèt Atmel-ICE kenbe aparèy sib la nan yon eta reset, ki ka esansyèl pou debogaj nan sèten senaryo. |

| VTG | 4 | 1 | Sib voltage referans. Atmel-ICE samples the target voltage sou peny sa a yo nan lòd yo pouvwa konvètisè yo nivo kòrèkteman. Atmel-ICE a tire mwens pase 3mA nan pin sa a nan mòd debugWIRE ak mwens pase 1mA nan lòt mòd. |

| GND | 2, 10 | 3, 5, 9 | Tè. Tout dwe konekte pou asire ke Atmel-ICE ak aparèy sib la pataje menm referans tè a. |

4.4.3.SPI Entèfas Fizik

Nan-System Programming itilize SPI entèn Atmel AVR sib la (Serial Peripheral Interface) pou telechaje kòd nan memwa flash ak EEPROM. Li se pa yon koòdone debogaj. Lè w ap desine yon PCB aplikasyon, ki gen ladan yon AVR ak koòdone SPI a, yo ta dwe itilize pinout la jan yo montre nan figi ki anba a.

Figi 4-10. SPI Header Pinout 4.4.4. Konekte ak yon sib SPI

4.4.4. Konekte ak yon sib SPI

Pinout rekòmande pou konektè SPI 6-pin yo montre nan Figi 4-10.

Koneksyon nan yon header 6-pin 100-mil SPI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil SPI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header SPI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

![]() Enpòtan:

Enpòtan:

Koòdone SPI a efektivman enfim lè debugWIRE pèmèt fuse (DWEN) pwograme, menm si SPIEN fuse tou pwograme. Pou re-aktive koòdone SPI a, yo dwe bay lòd 'enfim debugWIRE' pandan y ap nan yon sesyon debogaj debugWIRE. Enfim debugWIRE nan fason sa a mande pou fuse SPIEN a deja pwograme. Si Atmel Studio echwe pou enfim debugWIRE, li posib paske SPIEN fuse a PA pwograme. Si sa a se ka a, li nesesè yo sèvi ak yon wo-voltage pwogramasyon koòdone pou pwogram SPIEN fuse a.

![]() Info:

Info:

Se koòdone SPI a souvan refere yo kòm "ISP", depi li te premye koòdone nan pwogramasyon nan sistèm sou pwodwi Atmel AVR. Lòt koòdone yo disponib kounye a pou nan pwogramasyon nan sistèm.

Tablo 4-11. Atmel-ICE SPI Pin Mapping

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

SPI pinout |

| PIN 1 (TCK) | SCK | 1 | 3 |

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | MISO | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | / RESET | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | MOSI | 9 | 4 |

| PIN 10 (GND) | 0 |

4.4.5. PDI

Entèfas Pwogram ak Debug (PDI) se yon koòdone Atmel propriétaires pou pwogram ekstèn ak debogaj sou chip nan yon aparèy. PDI Physical se yon koòdone 2-pin ki bay yon kominikasyon synchrone demi-duplex bi-direksyon ak aparèy sib la.

Lè w ap desine yon PCB aplikasyon, ki gen ladann yon Atmel AVR ak koòdone PDI a, yo ta dwe itilize pinout yo montre nan figi ki anba a. Lè sa a, youn nan adaptè 6-pin yo bay ak twous Atmel-ICE yo ka itilize pou konekte sond Atmel-ICE la ak PCB aplikasyon an.

Figi 4-11. PDI Header Pinout 4.4.6.Konekte ak yon sib PDI

4.4.6.Konekte ak yon sib PDI

Pinout rekòmande pou konektè PDI 6-pin yo montre nan Figi 4-11.

Koneksyon nan yon header 6-pin 100-mil PDI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 100-mil.

Koneksyon nan yon header 6-pin 50-mil PDI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header PDI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande kat koneksyon, jan sa dekri nan tablo ki anba a.

![]() Enpòtan:

Enpòtan:

Pinout ki nesesè yo diferan de JTAGICE mkII JTAG sonde, kote PDI_DATA konekte ak zepeng 9. Atmel-ICE konpatib ak pinout Atmel-ICE, J.TAGICE3, AVR ONE!, ak AVR Dragon™ pwodwi yo.

Tablo 4-12. Atmel-ICE PDI Pin Mapping

|

Atmel-ICE AVR pò pin |

Pin sib | Mini-kalma PIN |

Atmel STK600 PDI pinout |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | PDI_DATA | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | PDI_CLK | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

4.4.7. Entèfas fizik UPDI

Pwogram Inifye ak Entèfas Debug (UPDI) se yon koòdone propriétaire Atmel pou pwogramasyon ekstèn ak debogaj sou chip nan yon aparèy. Li se yon siksesè nan koòdone fizik PDI 2-fil, ki jwenn sou tout aparèy AVR XMEGA. UPDI se yon koòdone yon sèl-fil ki bay yon kominikasyon asynchrone demi-duplex bi-direksyon ak aparèy sib la pou rezon pwogramasyon ak debogaj.

Lè w ap desine yon PCB aplikasyon, ki gen ladann yon Atmel AVR ak koòdone UPDI a, yo ta dwe itilize pinout yo montre anba a. Lè sa a, youn nan adaptè 6-pin yo bay ak twous Atmel-ICE yo ka itilize pou konekte sond Atmel-ICE la ak PCB aplikasyon an.

Figi 4-12. UPDI Header Pinout 4.4.7.1 UPDI ak / RESET

4.4.7.1 UPDI ak / RESET

Koòdone nan yon sèl-fil UPDI kapab yon peny dedye oswa yon peny pataje, tou depann de aparèy la AVR sib. Konsilte fèy done aparèy la pou plis enfòmasyon.

Lè koòdone UPDI a sou yon peny pataje, peny la ka configuré pou swa UPDI, / RESET, oswa GPIO lè w mete RSTPINCFG [1:0] yo.

Fyouz RSTPINCFG[1:0] yo gen konfigirasyon sa yo, jan sa dekri nan fichye a. Enplikasyon pratik chak chwa yo bay isit la.

Tablo 4-13. RSTPINCFG[1:0] Konfigirasyon Fuse

| RSTPINCFG[1:0] | Konfigirasyon |

Itilizasyon |

| 00 | GPIO | Objektif jeneral I/O PIN. Pou jwenn aksè nan UPDI, yo dwe aplike yon batman 12V sou pin sa a. Pa gen okenn sous reset ekstèn ki disponib. |

| 01 | UPDI | Dedye pwogramasyon ak debogaj PIN. Pa gen okenn sous reset ekstèn ki disponib. |

| 10 | Reyajiste | Reyajiste opinyon siyal. Pou jwenn aksè nan UPDI, yo dwe aplike yon batman 12V sou pin sa a. |

| 11 | Rezève | NA |

Nòt: Pi ansyen aparèy AVR yo gen yon koòdone pwogramasyon, ke yo rekonèt kòm "High-Voltage Programming” (tou de seri seri ak paralèl egziste.) An jeneral, koòdone sa a mande pou 12V aplike nan / RESET la pandan sesyon pwogramasyon an. Koòdone UPDI a se yon koòdone totalman diferan. PIN UPDI a se prensipalman yon PIN pwogramasyon ak debogaj, ki ka fusion pou gen yon fonksyon altènatif (/RESET oswa GPIO). Si yo chwazi fonksyon altènatif la, yo mande yon batman 12V sou pin sa a pou kapab re-aktive fonksyonalite UPDI a.

Nòt: Si yon konsepsyon mande pou pataje siyal UPDI a akòz kontrent PIN, etap yo dwe pran yo nan lòd asire ke aparèy la ka pwograme. Pou asire ke siyal UPDI a ka fonksyone kòrèkteman, osi byen ke pou fè pou evite domaj nan eleman ekstèn soti nan batman kè a 12V, li rekòmande dekonekte nenpòt eleman sou pin sa a lè w ap eseye debogaj oswa pwograme aparèy la. Sa a ka fè lè l sèvi avèk yon rezistans 0Ω, ki monte pa default epi retire oswa ranplase pa yon header peny pandan y ap debogaj. Konfigirasyon sa a efektivman vle di ke pwogramasyon yo ta dwe fè anvan monte aparèy la.

![]() Enpòtan: Atmel-ICE pa sipòte 12V sou liy UPDI a. Nan lòt mo, si PIN UPDI a te configuré kòm GPIO oswa RESET Atmel-ICE la pa pral kapab pèmèt koòdone UPDI a.

Enpòtan: Atmel-ICE pa sipòte 12V sou liy UPDI a. Nan lòt mo, si PIN UPDI a te configuré kòm GPIO oswa RESET Atmel-ICE la pa pral kapab pèmèt koòdone UPDI a.

4.4.8.Konekte ak yon sib UPDI

Pinout rekòmande pou konektè UPDI 6-pin yo montre nan Figi 4-12.

Koneksyon nan yon header UPDI 6-pin 100-mil

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header UPDI 100-mil estanda.

Koneksyon nan yon header UPDI 6-pin 50-mil

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header UPDI estanda 50-mil.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Twa koneksyon obligatwa, jan sa dekri nan tablo ki anba a.

Tablo 4-14. Atmel-ICE UPDI Pin Mapping

| Atmel-ICE AVR pò pin | Pin sib | Mini-kalma PIN |

Atmel STK600 UPDI pinout |

| PIN 1 (TCK) | 1 | ||

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | UPDI_DATA | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | [/RESET sans] | 6 | 5 |

| PIN 7 (Pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

4.4.9 TPI Entèfas Fizik

TPI se yon koòdone pwogramasyon sèlman pou kèk aparèy AVR ATtiny. Li se pa yon koòdone debogaj, ak aparèy sa yo pa gen kapasite OCD. Lè w ap desine yon PCB aplikasyon ki gen ladan yon AVR ak koòdone TPI a, yo ta dwe itilize pinout yo montre nan figi ki anba a.

Figi 4-13. TPI Header Pinout 4.4.10.Konekte ak yon sib TPI

4.4.10.Konekte ak yon sib TPI

Pinout rekòmande pou konektè TPI 6-pin yo montre nan Figi 4-13.

Koneksyon nan yon header 6-pin 100-mil TPI

Sèvi ak tiyo 6-pin 100-mil sou kab plat la (ki enkli nan kèk twous) pou konekte avèk yon header estanda 100-mil TPI.

Koneksyon nan yon header 6-pin 50-mil TPI

Sèvi ak tablo adaptè a (ki enkli nan kèk twous) pou konekte avèk yon header estanda 50-mil TPI.

Koneksyon nan yon header koutim 100-mil

Yo ta dwe itilize kab 10-pin mini-kalma pou konekte ant pò konektè Atmel-ICE AVR a ak tablo sib la. Yo mande sis koneksyon, jan sa dekri nan tablo ki anba a.

Tablo 4-15. Atmel-ICE TPI Pin Map

| Atmel-ICE AVR pò pins | Pin sib | Mini-kalma PIN |

TPI pinout |

| PIN 1 (TCK) | LÒJ | 1 | 3 |

| PIN 2 (GND) | GND | 2 | 6 |

| PIN 3 (TDO) | DONE | 3 | 1 |

| PIN 4 (VTG) | VTG | 4 | 2 |

| PIN 5 (TMS) | 5 | ||

| PIN 6 (nSRST) | / RESET | 6 | 5 |

| PIN 7 (pa konekte) | 7 | ||

| PIN 8 (nTRST) | 8 | ||

| PIN 9 (TDI) | 9 | ||

| PIN 10 (GND) | 0 |

4.4.11. Debogaj avanse (AVR JTAG /debugWIRE aparèy)

I/O periferik

Pifò periferik I/O yo ap kontinye kouri menmsi ekzekisyon pwogram nan sispann pa yon breakpoint. Egzample: Si yo rive nan yon breakpoint pandan yon transmisyon UART, transmisyon an pral fini ak korespondan Bits mete. Drapo a TXC (transmèt konplè) pral mete epi yo pral disponib nan pwochen etap la nan kòd la menm si nòmalman li ta rive pita nan yon aparèy aktyèl.

Tout modil I/O ap kontinye kouri nan mòd sispann ak de eksepsyon sa yo:

- Revèy / Counters (konfigurab lè l sèvi avèk front-end lojisyèl an)

- Watchdog Timer (toujou sispann pou anpeche reset pandan debogaj)

Single Stepping I/O aksè

Depi I/O kontinye ap kouri nan mòd sispann, yo ta dwe pran prekosyon pou evite sèten pwoblèm distribisyon. Pou egzanpample, kòd la:

Lè w ap kouri kòd sa a nòmalman, rejis TEMP a pa t ap li 0xAA paske done yo pa t 'ankò te bloke fizikman sou peny la lè li ye.ampki te dirije pa operasyon IN. Yon enstriksyon NOP dwe mete ant enstriksyon OUT ak IN pou asire ke valè kòrèk la prezan nan rejis PIN la.

Sepandan, lè yon sèl etap fonksyon sa a nan OCD a, kòd sa a ap toujou bay 0xAA nan rejis PIN la depi I / O a ap kouri nan vitès plen menm lè nwayo a sispann pandan sèl etap la.

Selibatè etap ak distribisyon

Sèten rejis bezwen li oswa ekri nan yon kantite sik bay apre pèmèt yon siyal kontwòl. Depi I/O revèy la ak periferik yo kontinye ap kouri a tout vitès nan mòd sispann, yon sèl etap nan kòd sa a pa pral satisfè kondisyon yo distribisyon. Ant de etap sèl, revèy I/O ka te kouri dè milyon de sik. Pou siksè li oswa ekri rejis ak kondisyon distribisyon sa yo, tout sekans li oswa ekri yo ta dwe fèt kòm yon operasyon atomik kouri aparèy la nan vitès plen. Sa a ka fè lè w sèvi ak yon makro oswa yon apèl fonksyon pou egzekite kòd la, oswa itilize fonksyon kouri-a-kursè nan anviwònman an debogaj.

Aksè rejis 16-bit

Anjeneral, periferik Atmel AVR yo genyen plizyè rejis 16-bit ki ka jwenn aksè atravè otobis done 8-bit (egzanp: TCNTn nan yon revèy 16-bit). Ou dwe jwenn aksè nan rejis 16-bit la lè l sèvi avèk de operasyon lekti oswa ekri. Kraze nan mitan yon aksè 16-bit oswa yon sèl etap nan sitiyasyon sa a ka lakòz valè inègza.

Aksè restriksyon nan enskri I/O

Sèten rejis pa ka li san yo pa afekte kontni yo. Rejis sa yo gen ladan yo ki gen drapo yo efase pa lekti, oswa rejis done tanpon (egzanp: UDR). Front-end lojisyèl an ap anpeche lekti rejis sa yo lè yo nan mòd sispann pou prezève nati a ki pa pèsistan nan debogaj OCD. Anplis de sa, kèk rejis pa ka ekri san danje san efè segondè rive - rejis sa yo se lekti sèlman. Pou egzanpample:

- Rejis drapo yo, kote yo efase yon drapo lè w ekri '1' nan nenpòt Rejis sa yo li sèlman.

- Rejis UDR ak SPDR pa ka li san yo pa afekte eta modil la. Rejis sa yo pa

4.4.12. Konsiderasyon espesyal megaAVR

Lojisyèl breakpoints

Piske li gen yon vèsyon byen bonè nan modil OCD a, ATmega128[A] pa sipòte itilizasyon ansèyman BREAK pou breakpoints lojisyèl.

JTAG revèy

Frekans revèy sib la dwe espesifye avèk presizyon nan front-end lojisyèl an anvan yo kòmanse yon sesyon debug. Pou rezon senkronizasyon, JTAG Siyal TCK dwe mwens pase yon katriyèm nan frekans revèy sib la pou debogaj serye. Lè w ap pwograme atravè JTAG koòdone, frekans TCK a limite pa Rating frekans maksimòm aparèy sib la, epi li pa frekans aktyèl la revèy yo te itilize.

Lè w ap itilize osilator entèn RC a, ou dwe konnen frekans lan ka varye de aparèy a aparèy epi li afekte pa tanperati ak V.CC chanjman. Fè konsèvatif lè w presize frekans revèy sib la.

JTAGEN ak OCDEN fusibles

J laTAG koòdone pèmèt lè l sèvi avèk JTAGEN fuse, ki pwograme pa defo. Sa pèmèt aksè nan JTAG koòdone pwogramasyon. Atravè mekanis sa a, OCDEN fuse ka pwograme (pa default OCDEN pa pwograme). Sa a pèmèt aksè nan OCD a nan lòd yo fasilite debogaj aparèy la. Front-end lojisyèl an ap toujou asire ke fusible OCDEN a pa pwograme lè w ap mete fen nan yon sesyon, kidonk limite konsomasyon enèji ki pa nesesè pa modil OCD a. Si JTAGEN fuse se san entansyonèlman enfim, li ka sèlman re-aktive lè l sèvi avèk SPI oswa High Voltage metòd pwogramasyon.

Si JTAGEN fuse pwograme, JTAG koòdone ka toujou enfim nan firmwèr lè w mete ti jan JTD la. Sa a pral rann kòd un-debuggable, epi yo pa ta dwe fè lè eseye yon sesyon debug. Si kòd sa a deja ap egzekite sou aparèy Atmel AVR a lè w ap kòmanse yon sesyon debogaj, Atmel-ICE ap afime liy RESET la pandan y ap konekte. Si liy sa a branche kòrèkteman, li pral fòse aparèy AVR sib la nan reset, kidonk pèmèt yon JTAG koneksyon.

Si JTAG koòdone pèmèt, JTAG broch pa ka itilize pou fonksyon pin altènatif. Yo pral rete dedye JTAG broch jiskaske swa JTAG koòdone enfim lè w mete ti jan JTD ki soti nan kòd pwogram lan, oswa lè w netwaye JTAGEN fuse atravè yon koòdone pwogramasyon.

![]() Konsèy:

Konsèy:

Asire w ou tcheke kaz "itilize ekstèn reset" nan tou de dyalòg pwogramasyon an ak dyalòg opsyon debug yo nan lòd yo pèmèt Atmel-ICE a revandike liy RESET la epi re-pèmèt J la.TAG koòdone sou aparèy ki ap kouri kòd ki enfim JTAG koòdone pa mete JTD bit la.

Evènman IDR/OCDR

IDR (In-out Data Register) konnen tou kòm OCDR (On Chip Debug Register), epi debugger la itilize anpil pou li ak ekri enfòmasyon nan MCU a lè yo nan mòd sispann pandan yon sesyon debug. Lè pwogram aplikasyon an nan mòd kouri ekri yon byte done nan rejis OCDR aparèy AVR ke yo te debogaj la, Atmel-ICE li valè sa a epi li montre li nan fennèt mesaj devan lojisyèl an. Rejis OCDR a sondaj chak 50ms, kidonk ekri li nan yon frekans ki pi wo a PA bay rezilta serye. Lè aparèy AVR a pèdi kouran pandan y ap debogaj li, yo ka rapòte evènman OCDR ki pa bon. Sa rive paske Atmel-ICE ka toujou sondaj aparèy la kòm sib voltage gout pi ba pase volim opere minimòm AVR atage.

4.4.13. Konsiderasyon espesyal AVR XMEGA

OCD ak revèy

Lè MCU a antre nan mòd sispann, revèy OCD a itilize kòm revèy MCU. OCD revèy la se swa JTAG TCK si JTAG koòdone yo te itilize, oswa PDI_CLK la si yo te itilize koòdone PDI a.

I/O modil nan mòd sispann

Kontrèman ak aparèy megaAVR Atmel anvan yo, nan XMEGA modil I/O yo sispann nan mòd sispann. Sa vle di ke transmisyon USART yo pral entèwonp, revèy (ak PWM) ap sispann.

Pwen pyès ki nan konpitè

Gen kat konparatè breakpoint pyès ki nan konpitè - de konparatè adrès ak de konparatè valè. Yo gen sèten restriksyon:

- Tout breakpoints yo dwe nan menm kalite (pwogram oswa done)

- Tout pwen rupture done yo dwe nan menm zòn memwa (I/O, SRAM, oswa XRAM)

- Gen sèlman yon pwen breakpoint si yo itilize ranje adrès

Men diferan konbinezon yo ka mete:

- De sèl done oswa pwogram adrès breakpoints

- Youn done oswa adrès pwogram ranje breakpoint

- De sèl done adrès breakpoints ak yon sèl valè konpare

- Yon pwen rupture done ak ranje adrès, ranje valè, oswa toude

Atmel Studio ap di w si breakpoint a pa ka fikse, e poukisa. Point breakpoints done yo gen priyorite sou pwogram breakpoints, si breakpoints lojisyèl disponib.

Reset ekstèn ak PDI fizik

Koòdone fizik PDI a sèvi ak liy reset la kòm revèy. Pandan debogaj, pullup reset la ta dwe 10k oswa plis oswa yo dwe retire. Nenpòt kondansateur reset yo ta dwe retire. Lòt sous reset ekstèn yo ta dwe dekonekte.

Debogaj ak dòmi pou ATxmegaA1 rev H ak pi bonè

Yon ensèk te egziste sou vèsyon byen bonè nan aparèy ATxmegaA1 ki anpeche OCD a te pèmèt pandan y ap aparèy la te nan mòd dòmi sèten. Gen de solisyon pou re-pèmèt OCD:

- Ale nan Atmel-ICE la. Opsyon nan meni Zouti a epi pèmèt "Toujou aktive reset ekstèn lè w ap repwograme aparèy la".

- Fè yon efase chip

Mòd dòmi ki deklanche ensèk sa a se:

- Pouvwa-desann

- Pouvwa-sove

- Standby

- Pwolonje sibstiti

4.4.1.debugWIRE Konsiderasyon espesyal

PIN kominikasyon debugWIRE (dW) sitiye fizikman sou menm peny ak reset ekstèn (RESET). Se poutèt sa, yon sous reset ekstèn pa sipòte lè koòdone debugWIRE la pèmèt.

DebugWIRE Enable fuse (DWEN) dwe mete sou aparèy sib la pou koòdone debugWIRE fonksyone. Fyouz sa a pa defo pa pwograme lè aparèy Atmel AVR la anbake soti nan faktori a. Koòdone debugWIRE tèt li pa ka itilize pou mete fuse sa a. Yo nan lòd yo mete DWEN fuse a, yo dwe itilize mòd SPI a. Lojisyèl front-end la okipe sa otomatikman bay broch SPI ki nesesè yo konekte. Li kapab tou tabli lè l sèvi avèk pwogram SPI nan dyalòg pwogram Atmel Studio.

Swa: Eseye kòmanse yon sesyon debug sou pati debugWIRE la. Si koòdone debugWIRE la pa aktive, Atmel Studio ap ofri pou re-eseye, oswa eseye pèmèt debugWIRE lè l sèvi avèk pwogram SPI. Si w gen tout tèt SPI a konekte, debugWIRE pral pèmèt, epi yo pral mande w pou aktive pouvwa sou sib la. Sa a se obligatwa pou chanjman yo fuse yo dwe efikas.

Oswa: Louvri dyalòg pwogramasyon an nan mòd SPI, epi verifye si siyati a matche ak aparèy ki kòrèk la. Tcheke fuse DWEN pou pèmèt debugWIRE.

![]() Enpòtan:

Enpòtan:

Li enpòtan pou kite fusible SPIEN pwograme, fusible RSTDISBL pa pwograme! Pa fè sa a pral rann aparèy la kole nan mòd debugWIRE, ak High VoltagYo pral oblije pwogramasyon an pou retounen anviwònman DWEN.

Pou enfim koòdone debugWIRE, sèvi ak High Voltage pwogramasyon pou de-pwogram fusible DWEN la. Altènativman, sèvi ak koòdone debugWIRE tèt li pou enfim tèt li tanporèman, sa ki pral pèmèt pwogramasyon SPI pran plas, depi yo mete fuze SPIEN la.

![]() Enpòtan:

Enpòtan:

Si SPIEN fuse PA te rete pwograme, Atmel Studio pap ka fini operasyon sa a, ak High VoltagYo dwe itilize pwogramasyon yo.

Pandan yon sesyon debug, chwazi opsyon nan meni 'Enfim debugWIRE ak fèmen' nan meni 'Debug' la. DebugWIRE pral enfim tanporèman, epi Atmel Studio pral sèvi ak pwogram SPI pou retire pwogram DWEN fuse a.

Èske w gen fuse DWEN pwograme pèmèt kèk pati nan sistèm revèy la ap kouri nan tout mòd dòmi. Sa a pral ogmante konsomasyon pouvwa a nan AVR a pandan y ap nan mòd dòmi. Se poutèt sa, DWEN Fuse a ta dwe toujou enfim lè debugWIRE pa itilize.

Lè w ap desine yon PCB aplikasyon sib kote yo pral itilize debugWIRE, yo dwe fè konsiderasyon sa yo pou operasyon kòrèk:

- Rezistans rale sou liy dW/(RESET) pa dwe pi piti (pi fò) pase 10kΩ. Rezistans rale-up la pa obligatwa pou fonksyonalite debugWIRE, depi zouti debugger la bay

- Nenpòt kondansateur estabilize ki konekte ak PIN RESET la dwe dekonekte lè w ap itilize debugWIRE, paske yo pral entèfere ak operasyon kòrèk nan koòdone la.

- Tout sous reset ekstèn oswa lòt chofè aktif sou liy RESET dwe dekonekte, paske yo ka entèfere ak operasyon kòrèk koòdone a.

Pa janm pwograme lock-bits yo sou aparèy la sib. Koòdone debugWIRE a mande pou yo netwaye lock-bits yo nan lòd yo fonksyone kòrèkteman.

4.4.15. debugWIRE Software Breakpoints

OCD debugWIRE la redwi anpil lè yo konpare ak megaAVR Atmel la (JTAG) OCD. Sa vle di ke li pa gen okenn konparatè pwogram ki disponib pou itilizatè a pou rezon debogaj. Youn nan konparezon sa yo egziste pou rezon operasyon kouri-a-kursè ak yon sèl-etap, men lòt pwen rupture itilizatè yo pa sipòte nan pyès ki nan konpitè.

Olye de sa, debogaj la dwe sèvi ak enstriksyon AVR BREAK la. Enstriksyon sa a ka mete nan FLASH, epi lè li chaje pou ekzekisyon li pral lakòz CPU AVR a antre nan mòd sispann. Pou sipòte breakpoints pandan debogaj, debugger la dwe mete yon enstriksyon BREAK nan FLASH nan pwen kote itilizatè yo mande yon breakpoint. Enstriksyon orijinal la dwe nan kachèt pou ranplase pita.